This work has also been supported by Science Foundation Ireland (SFI) and is co-funded under the European Regional Development Fund under Grant Number 13/RC/207.

#### Energy Harvesting ULP PMIC for Smart Sensor Node

Enerharv 2018 – Power Management

CFTD

Séamus O'Driscoll, Tim Daly, James McCarthy, Gerry McGlinchey, Ivan O'Connell, Michael Hayes

28<sup>th</sup> May 2018

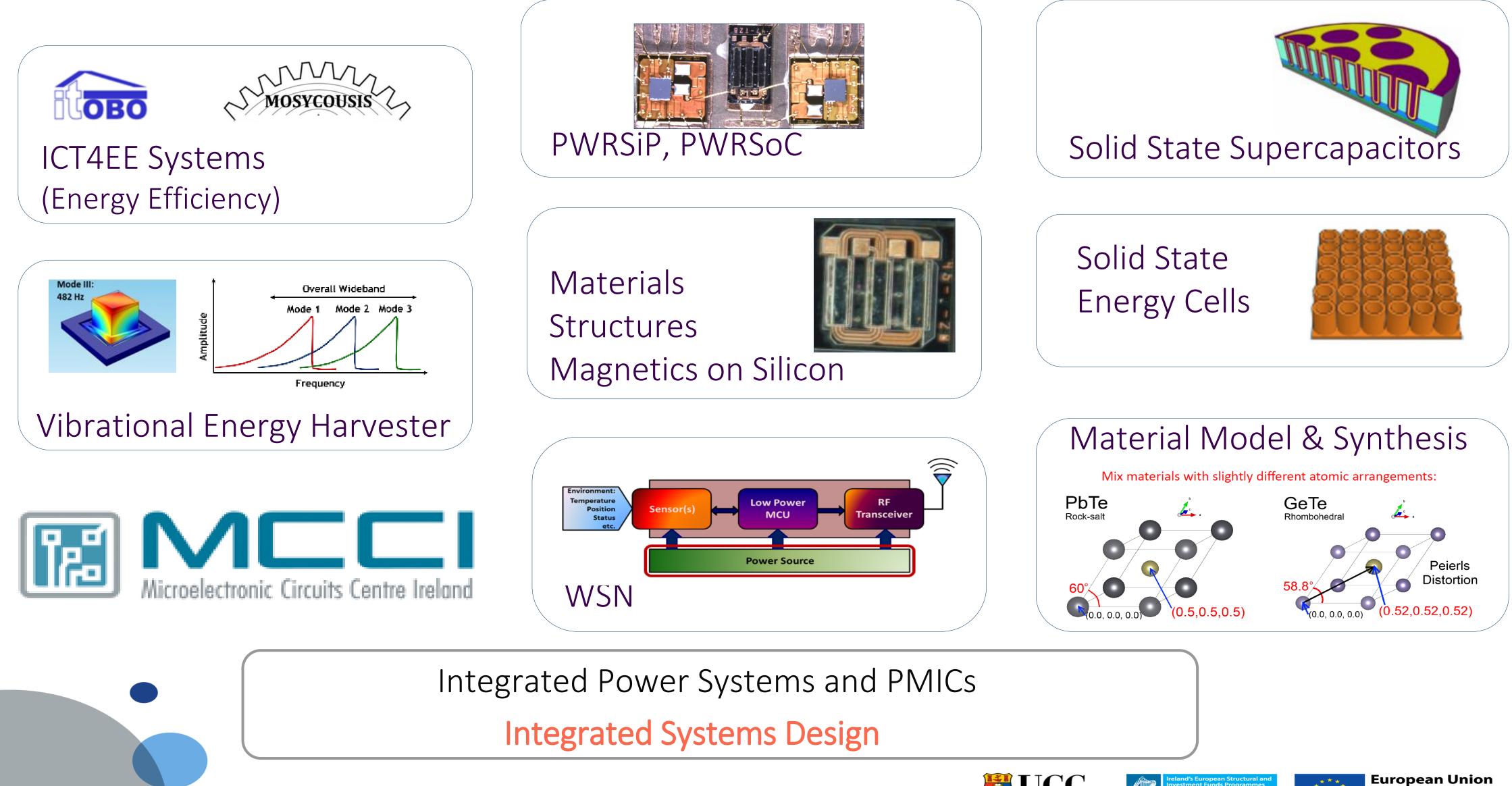

#### **On-Site Research Groups contributing to Energy Harvesting & PMIC Development**

**European Regional** Development Fund

#### Power Conversion & PMIC at Tyndall:

Smart Sensor Power Ambient Energy Harvesting Implantable Power Couplers, EMT

300W

0.3 W

DC-DC: POL, VR, SoC Switch Mode Inductor or Hybrid Topology Advanced Magnetic Component Designs 1-100M BEOL Wafer Scale RDL based Thin Film Magnetic Materials, Substrate Embeddable

(Highly) Integrated Power Conversion Systems

Power Manager IC - PMIC

GaNonCMOS PWRSiP, PWRSoC

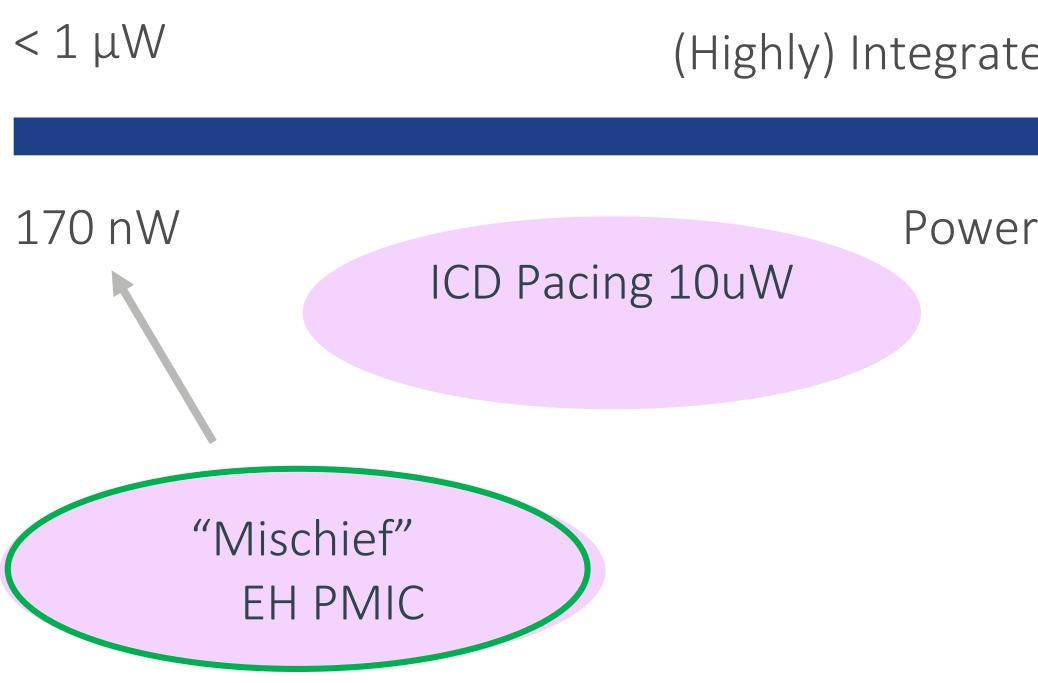

# Ultra Low Power (ULP) PMICs

- Low Bandwidth and Low Average Da systems

- Or

- Battery Life extension to 25+ years

#### Low Bandwidth and Low Average Data *"battery-less"* (maintenance-free)

Power and Energy Data points

Short-range (BLE) Wireless SoC Wearables - 1µA Idle with 32kHz & RTC ~2.4uW average for radio for heart rate profile – 4bytes/s for 1h/day

Ocular (retina) implant system @ IDD=50nA

*Hearing Aid DSP - <100uA/MIPs*

SOA Technology Solid State Storage on 1.5mm X 1.5mm die will provide ~15μW.h (10μm layer)

ICD Pacing Circuits 1-10uW

ADuCM4050 Signal Processor 40µA/MHz active & 680nA hibernate

#### Wide Dynamic Range & Heavily Duty Cycled Loads and Sources

Solar cells

- 100klux outdoors

- 10lux indoors

- Upto 10<sup>4</sup> dynamic range of available power

- sub-nA with low area cells

- We measure 10 lux under a bench, 300 lux in "brightly lit" room

- Solar Cell Dynamic Range 1x10<sup>4</sup> [Paidimarri et al, ISSCC '17]

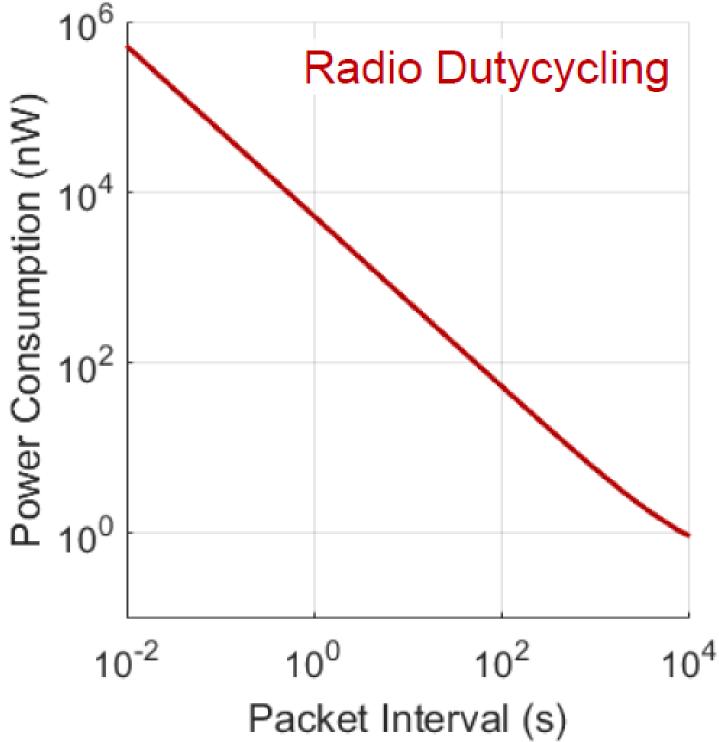

- Radio has 7.6x10<sup>7</sup> Dynamic Range [Paidimarri et al, ISSCC '15]

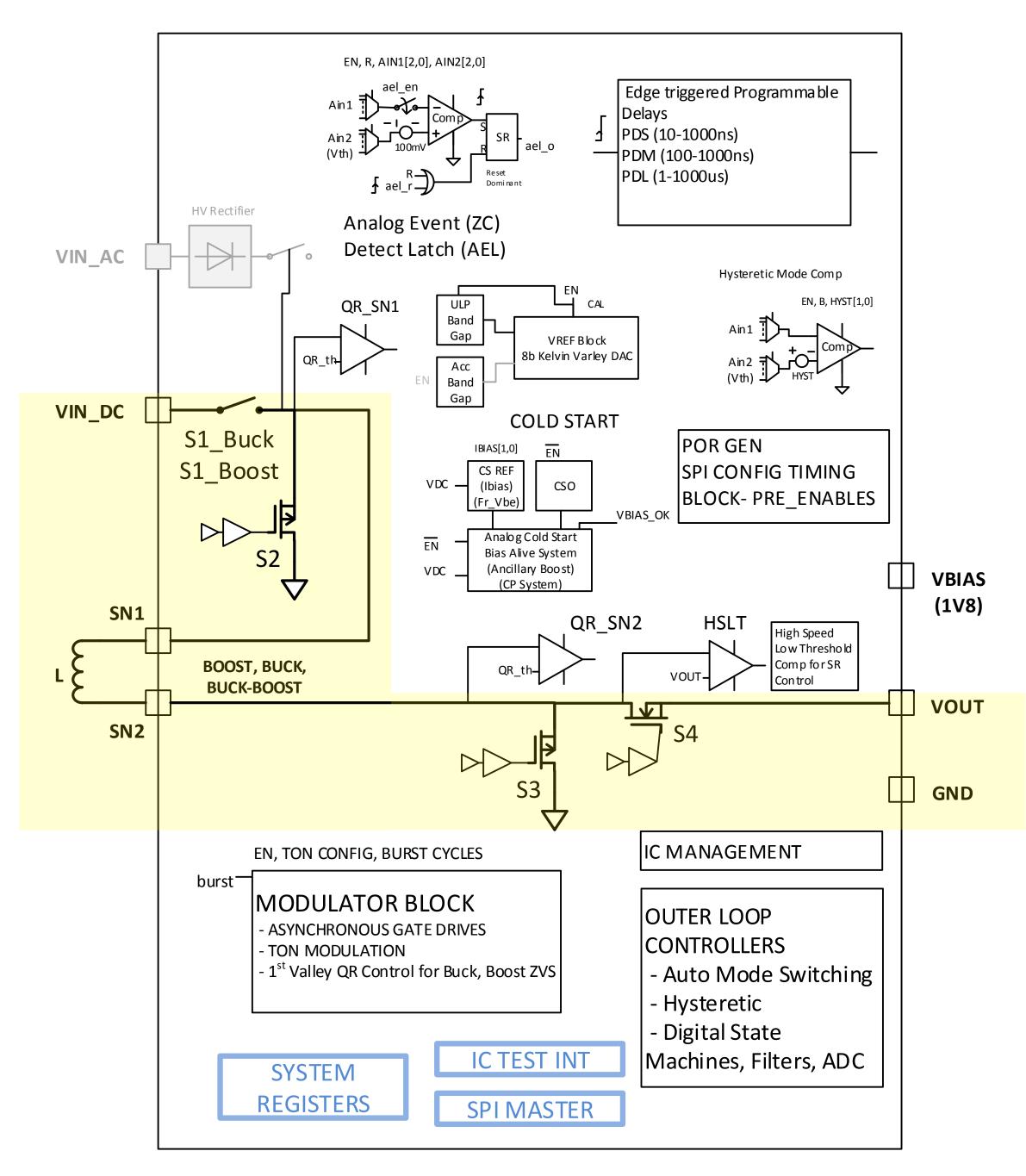

# **Control Silicon - ULP Wireless System Node** PMIC

Harvested Energy Conversion **Energy Storage Management Battery Management Regulated Voltages for the System**  System Controller Sensor Interface

- The PMIC is currently generally a discrete IC

PMIC Voltages, Silicon Requirements and Control are very compatible with radio

• Accordingly "Mischief" represents flexible, mixed-signal, ULP-PMIC platform IP offering

Radio RF

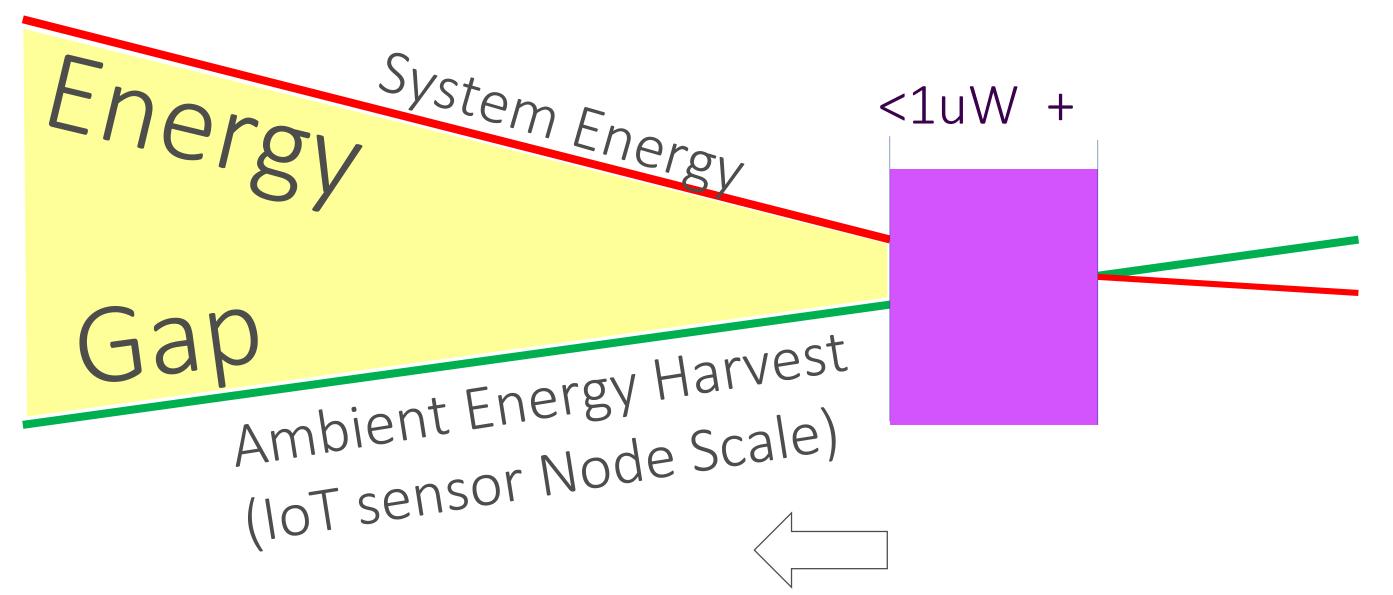

#### But at ULP level the smart sensor node *ideally requires a very high level of integration*

- Mixed-signal sensor interface circuits are very similar to those for energy source interaction and power control

- *Outer loop (tertiary) power control should ideally share resources with the system (host) controller.*

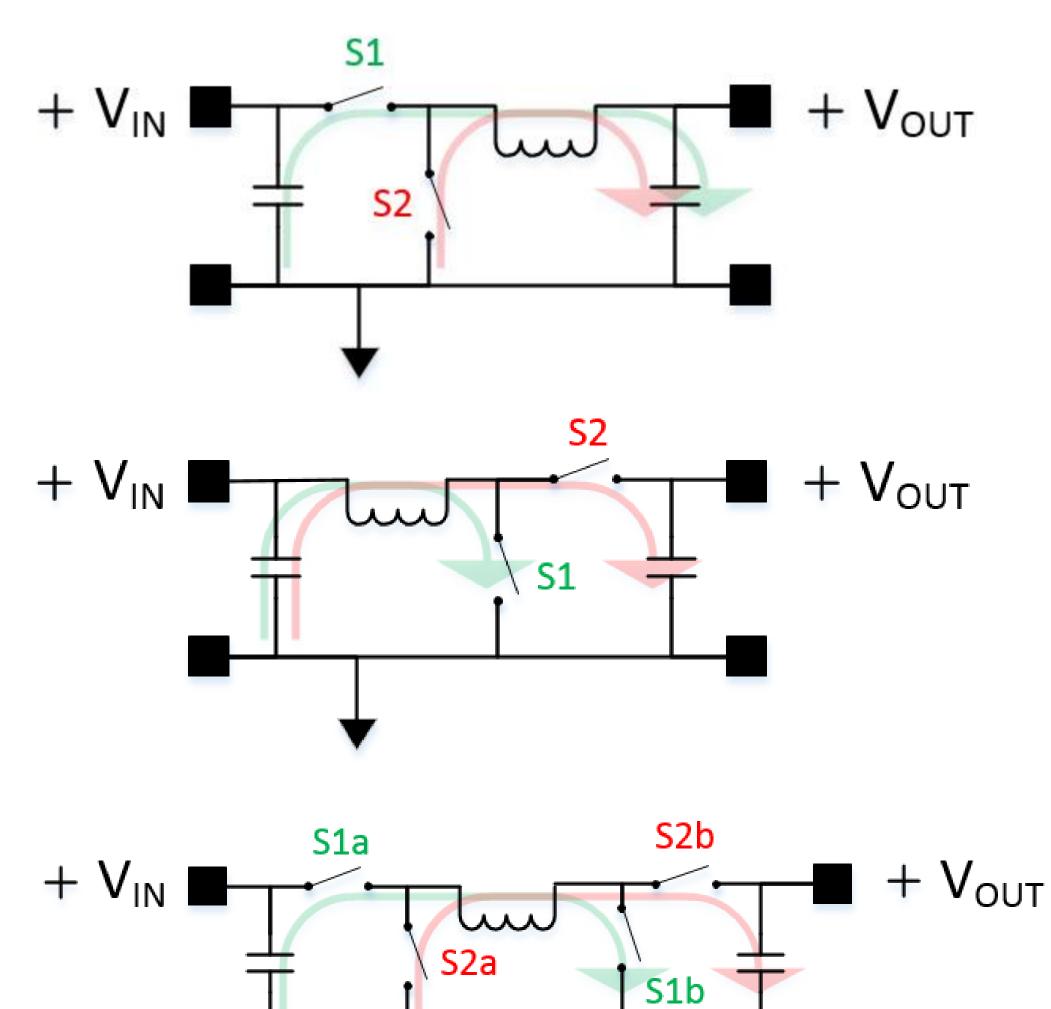

#### Switch Mode Inductor Topologies

#### Buck $V_{IN} > V_{OUT}$

Inductors are beautifully voltage compliant

Buck or Boost are more efficient than Buck-Boost

Inductors are large when looking for small  $\Delta i$

Boost  $V_{OUT} > V_{IN}$

**Buck-Boost**  $V_{OUT} <,> V_{IN}$

#### PMIC Platform IP Development Goals

Extend to sub -  $1\mu$ W for emerging MICRO, MESO and MESO

Emerging Smart Sensor Node Controllers such as ADuCM4050 (40µA/MHz active, 680nA in hibernate mode, rapid start)

Control flexibility to maximise energy transduction, energy storage and full-system energy efficiency

- for a variety of energy harvester types: PV, TEG, Piezo, Electromagnetic and Electret

- Bring advanced intelligent control to the space (digital and mixed-signal)

- Leverage the benefits of digital assisting analog for low quiescent current PMIC circuits and references

- Create flexible solution IP to address power management challenge for IoT devices

- Cater for multiple system voltages, multiple input-output ratios and extend input voltage range

- A lot of niche smart sensor applications will require dynamic and intelligent fit with:

- the application environment

- the sensor

- the radio

- the energy source nature, type, MPPT, impedance

- the storage

### Enabling High Value, Novel, Next Generation Features

of source and storage

Charge profile tuning to suit **emerging battery chemistries**

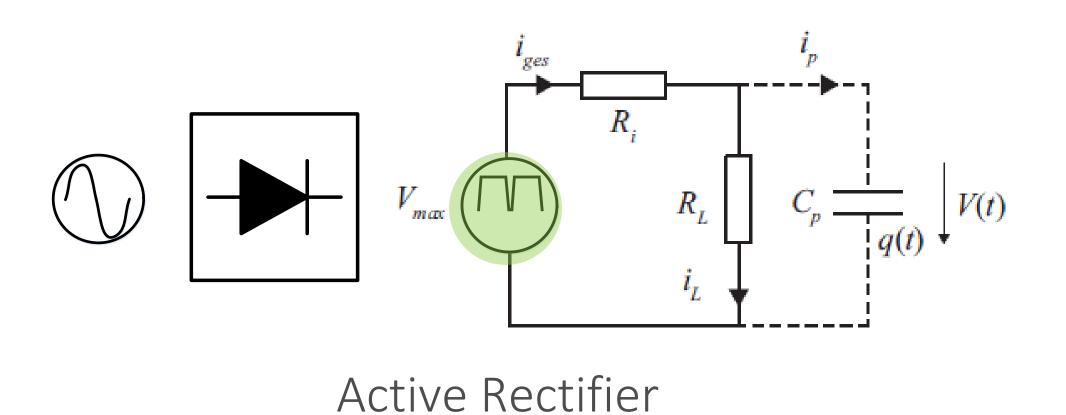

VEH is AC and will be by Active Rectifier & DC-DC or Power Factor Improvement or Hybrid

Piezoelectric, electret devices tend to be current source in nature Electromagnetic transduction tend to be voltage source in nature

- Digitised outer loop power/current set points for MPPT will enable features such as performance monitoring

Power Factor Improvement

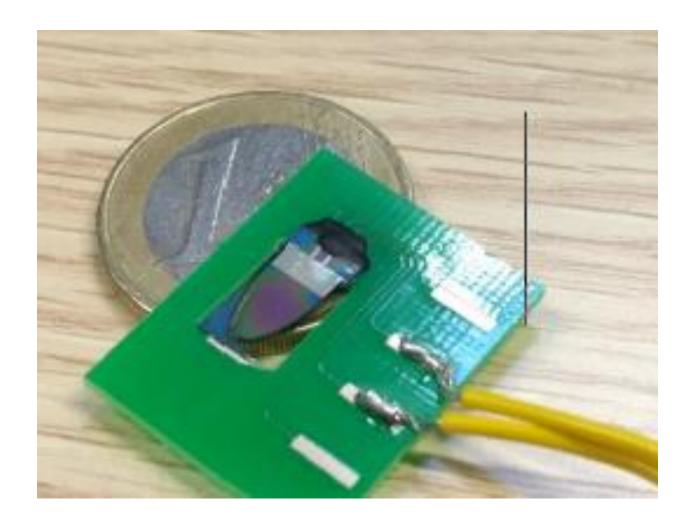

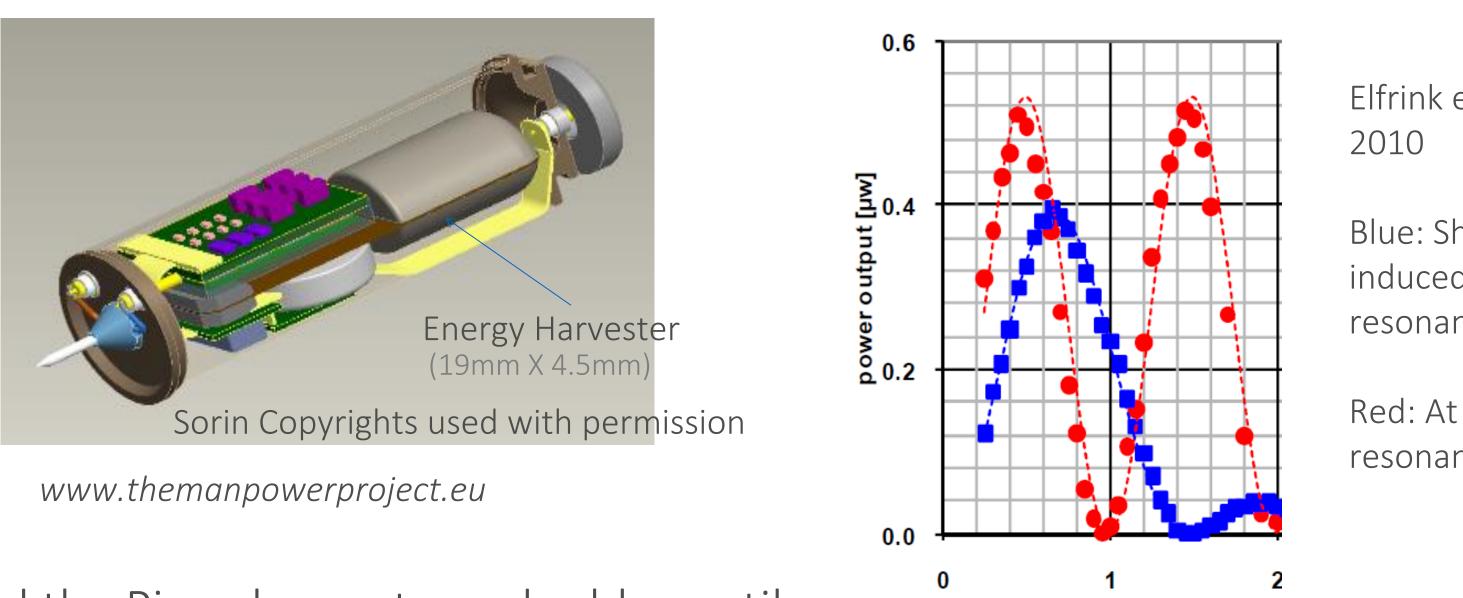

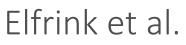

## ULP PIEZO Research – AIN Piezo Harvester

Leadless implantable – Tyndall created the Piezo harvester – double cantilever ~3uW (1-10V) average power operating at 60 bpm, fits inside a commercial leadless pacemaker. Off-resonance based on impulse acceleration method – MEMs compatible process

Substantial further improvements are possible and mixed signal control will add value

Maximise energy extraction during single shock excitation, as an example.

#### Piezo – Energy Extraction at Mechanical Vibration Frequency from a Capacitive Source

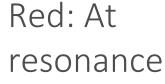

- At the vibration frequency  $(\Omega_M)$  facilitates ULP

- A quickly evolving variety of Active Rectifier, Conduction Angle Extension (Bias Flip, Parallel Synchronous Switch Harvesting on Inductor (P-SSHI)) or other Synchronous Charge Extraction (SECE) techniques.

"A 4µW-to-1mW Parallel-SSHI Rectifier for Piezoelectric Energy Harvesting of Periodic and Shock Excitations with Inductor Sharing, Cold Start-up and up to 681% Power Extraction Improvement", Daniel A. Sanchez et. al., ISSCC 2016

Current Source Generator results in Square Wave Voltage determined by MPPT Control of DC Voltage after the rectifier

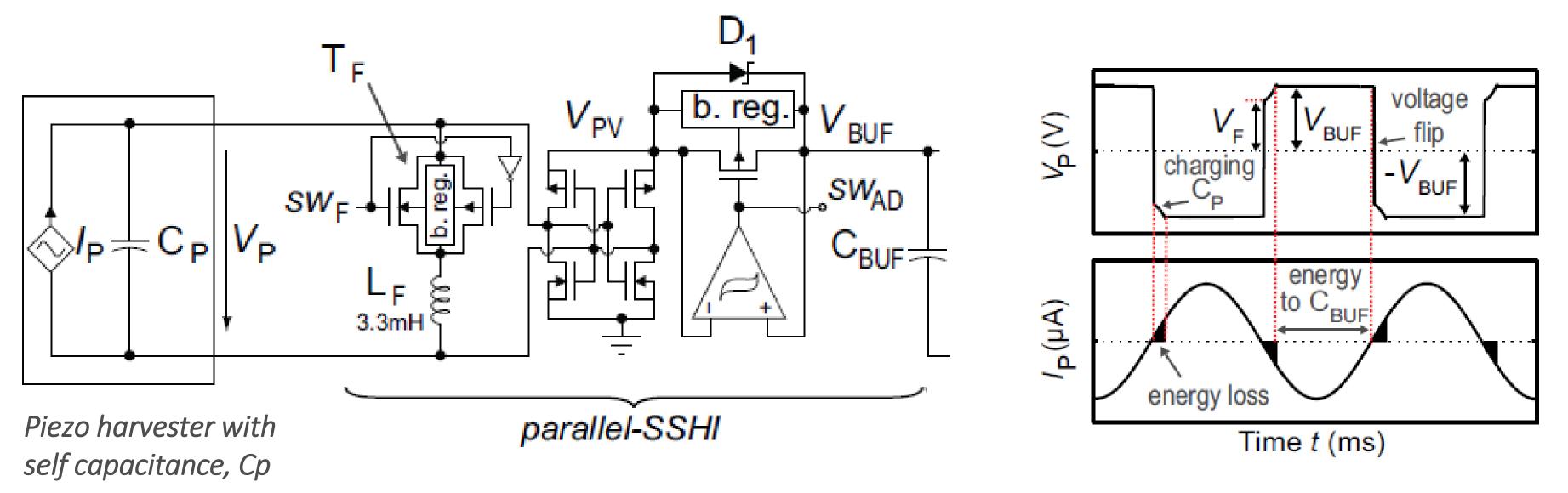

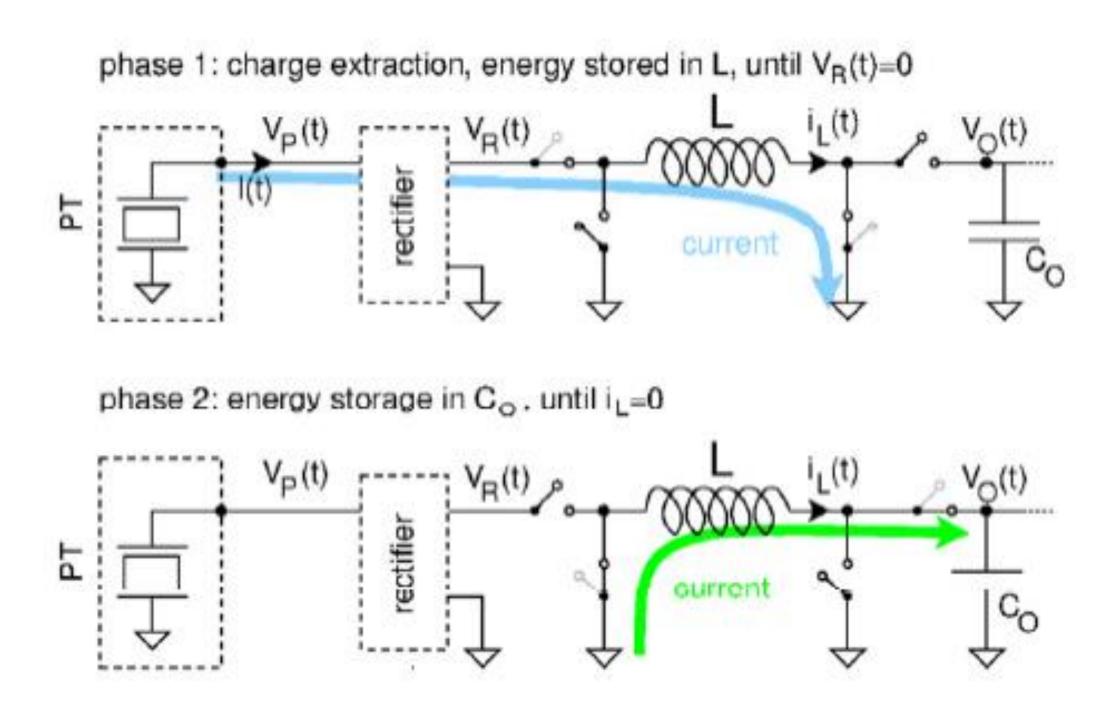

#### SECE Piezo Harvesting Circuit Example

EUROSENSORS 2014, the XXVIII edition of the conference series

#### Quasi-Synchronous Charge Extraction for Improved Energy Harvesting from Highly Coupled Piezoelectric Transducers

Aldo Romani\*, Matteo Filippi

University of Bologna, Via Venezia 52, Cesena 47521, Italy

This is a Buck-Boost Circuit operated synchronously with mechanical vibration to resonantly (efficiently) extract charge from the piezo capacitive source

All of these harvesting circuits benefit from:

- MPPT

- Analog Event Driven State Machines

- Digital Timing Curcuits

- High Speed Low Threshold Comparators

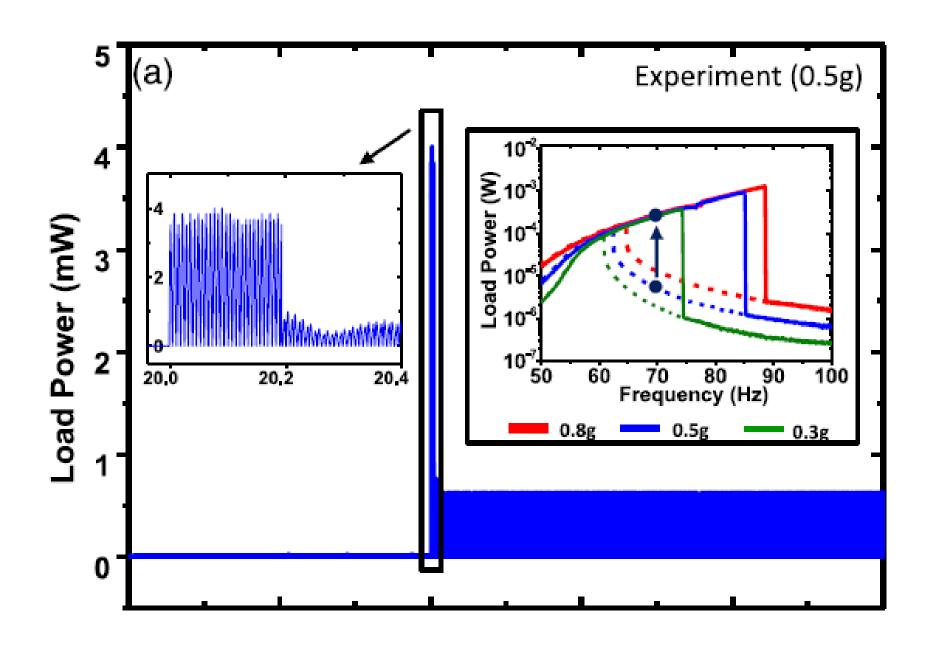

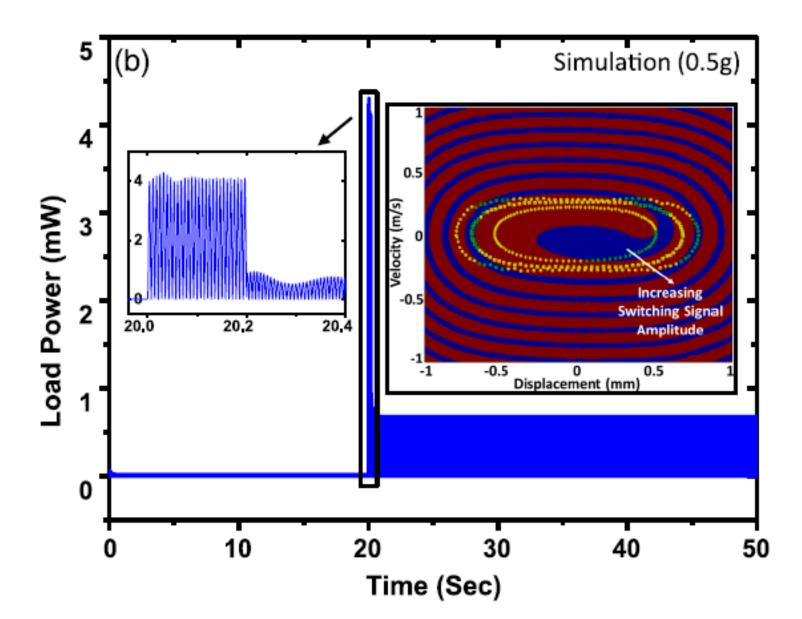

### Mechanical and Electrical Co-Design VEH

- Mechanical Non-Linearities added in transducer design +

- Non-Linear Electrical Stimuli to maintain high energy branch resonances

- Design for high reliability involves advanced packaging design

- Signal interaction, such as displacement, strain measurement

- Electrical techniques to increase reliability

"Surfing the high energy branch of nonlinear energy harvesters', D. Mallick, S. Roy, Phys. Rev. Lett., week ending 4 NOVEMBER 2016, claim **32 X**

Example for Electromagnetic VEH

There are analogous techniques for Piezo under review by IEEE MEMS

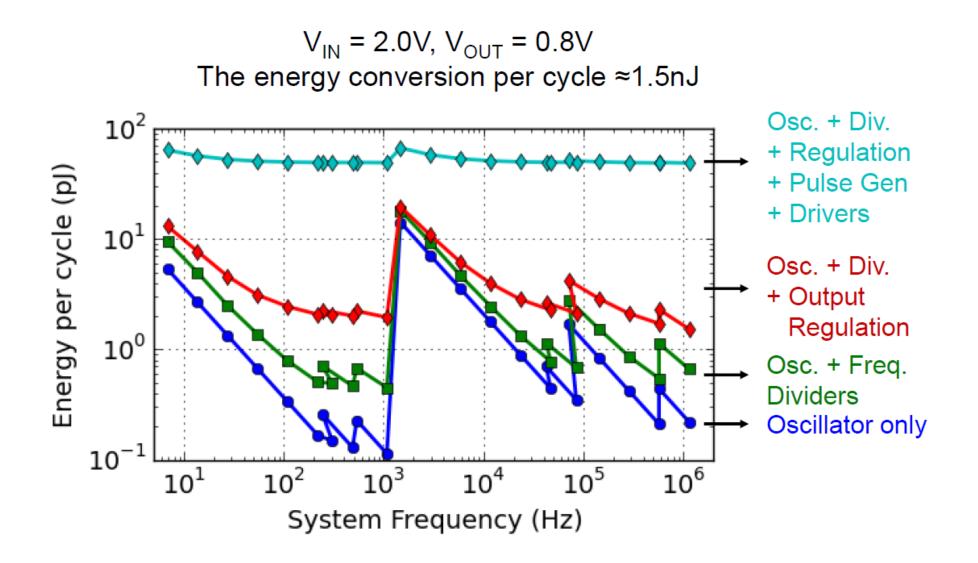

### Platform Circuit Design Philosophy

- Lowest Quiescent Current Blocks, in combination with:

- **Optimised Energy Transfer per Cycle**

- Frequency scalable or as required energy cycle transfer

- Efficient and Linear over wide dynamic range

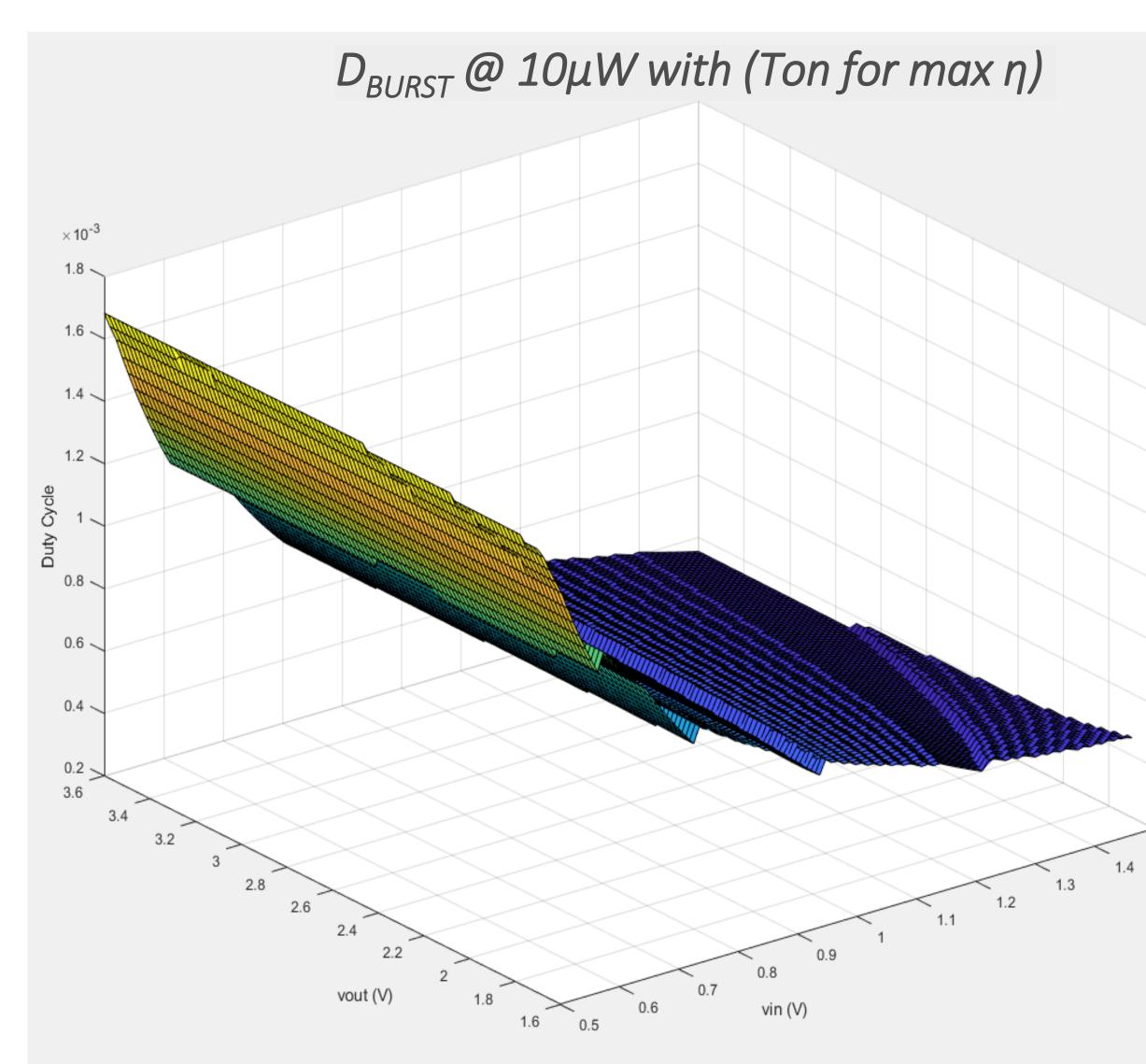

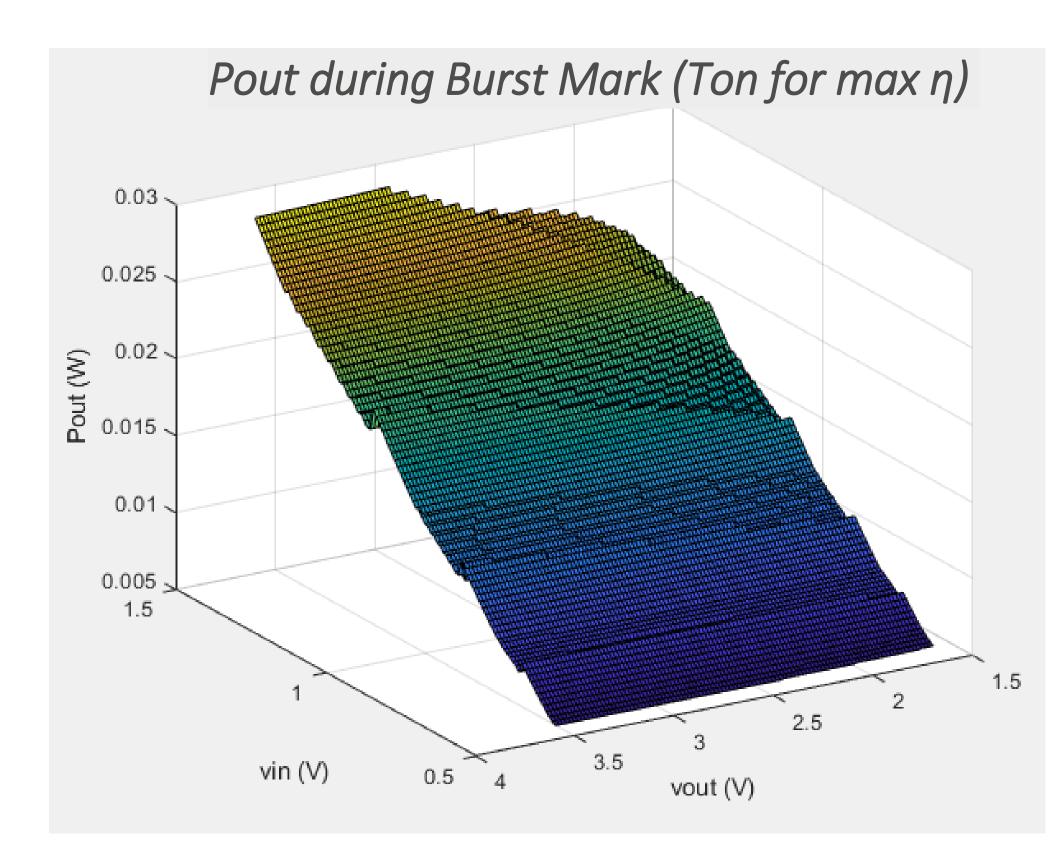

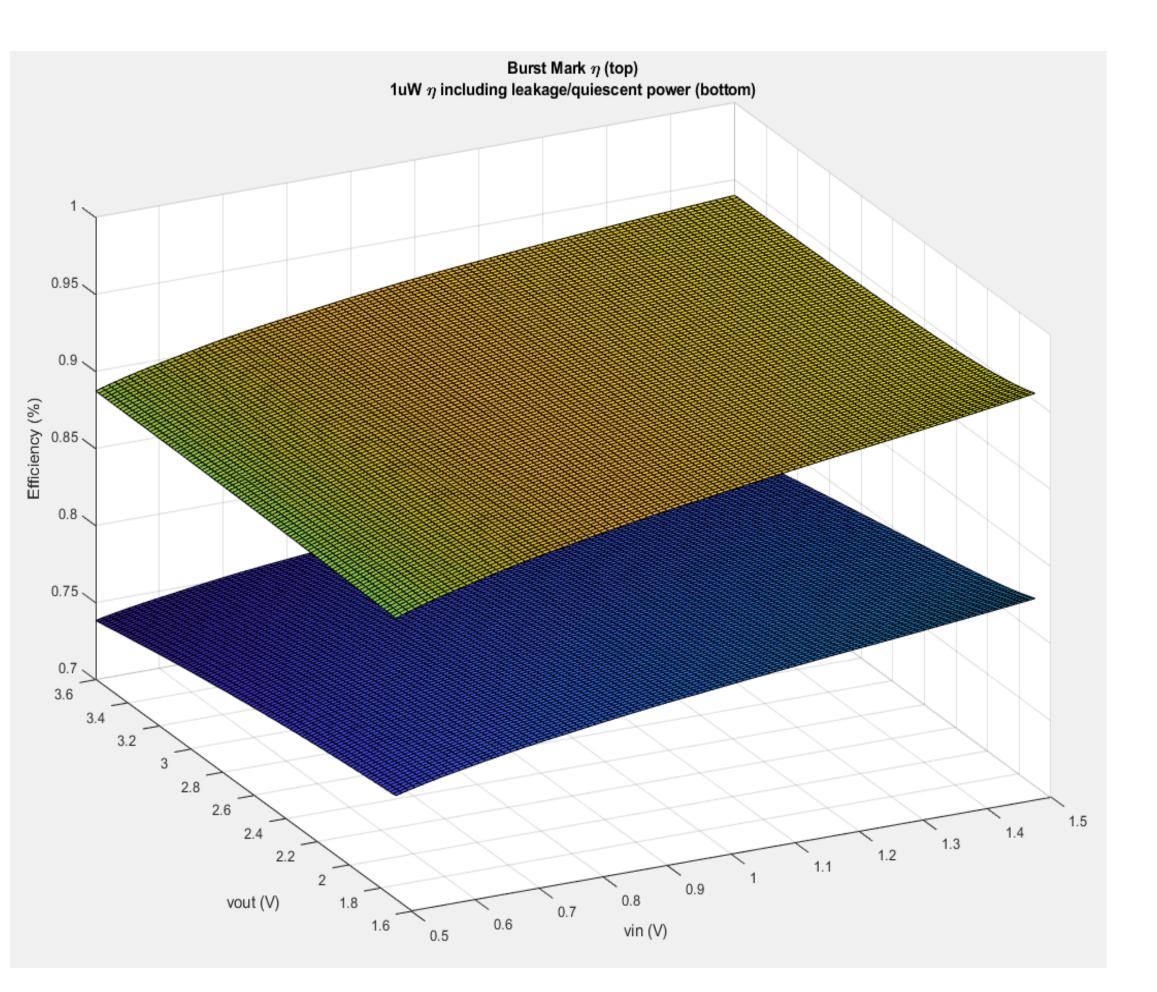

- Burst Mark-Space duty cycling and optimum cycles per Burst Mark

- Control functionality on demand Control power  $\infty$  burst frequency

- Inductor based Switch Mode

- Efficient at processing high energy per cycle

- Inductors are extremely compliant for wide voltage range

- Drawback is that large L value and low DCR (high RMS) is required => "very large" 22uH+ inductor - 4 x 4 x 1.8 mm (typical) size!

- **Buck or Boost** (Buck-Boost Capability) for conversion to **multiple system voltages**

- Very low Switching Loss for **high frequency**

- **SPI** Configurability

Time interleaving modes allows maximisation of efficiency and possible direct conversion to multiple system voltages

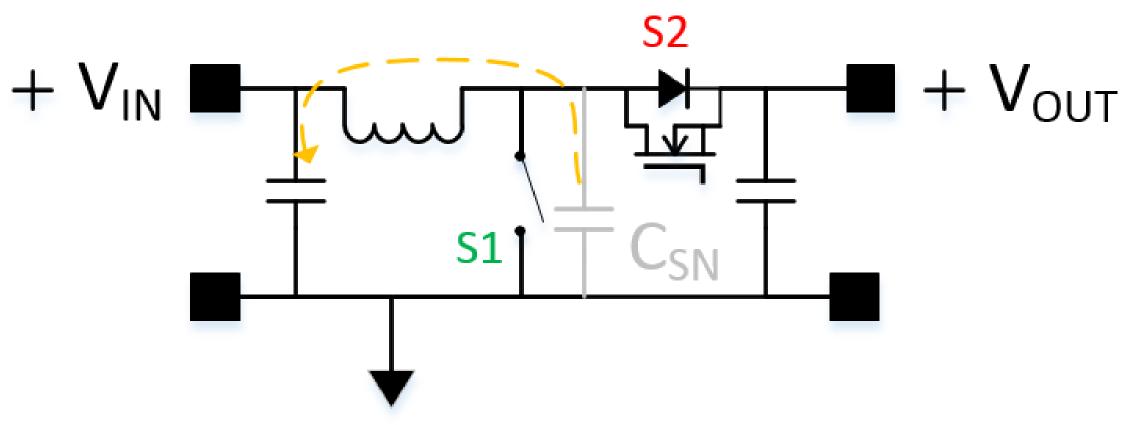

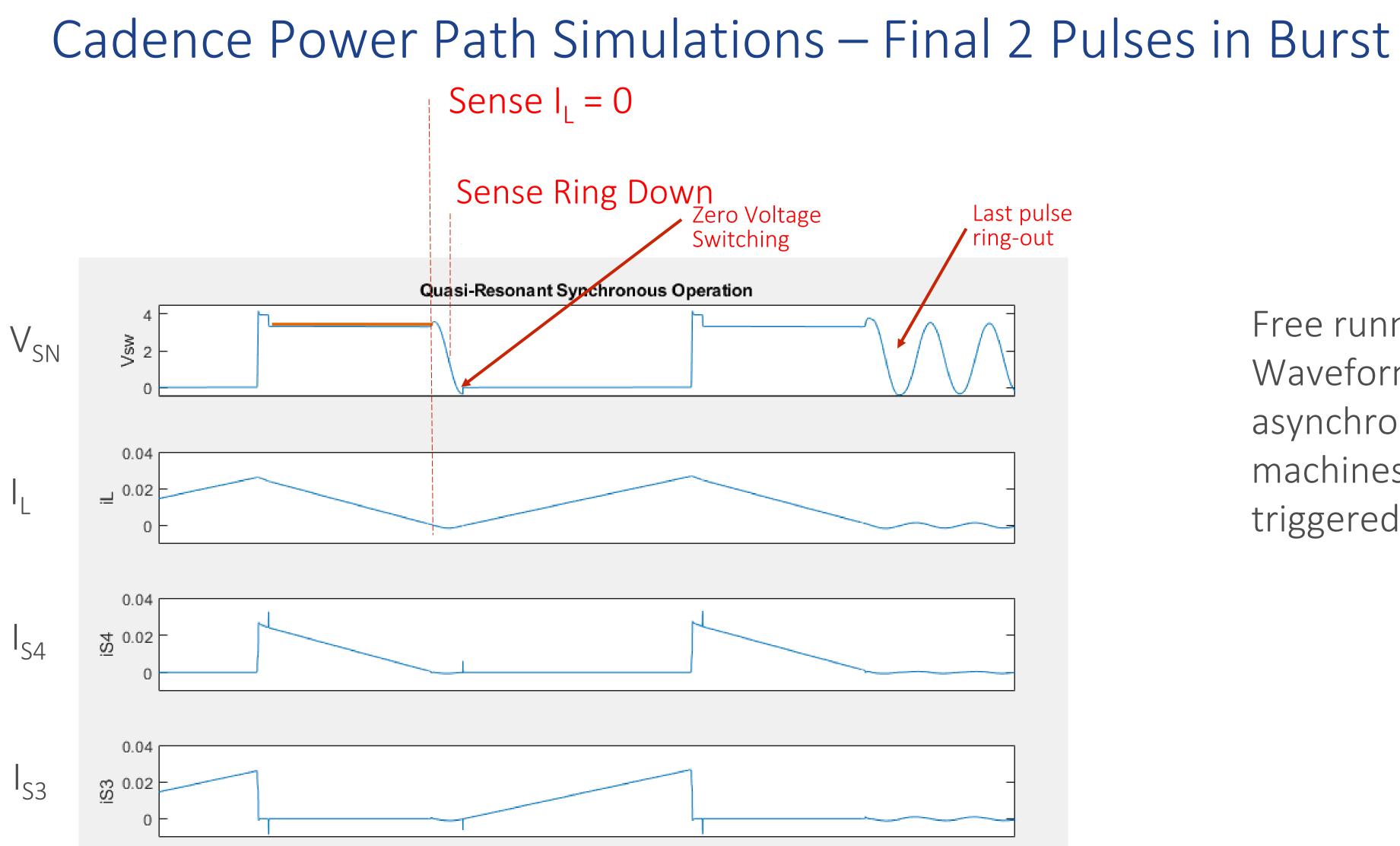

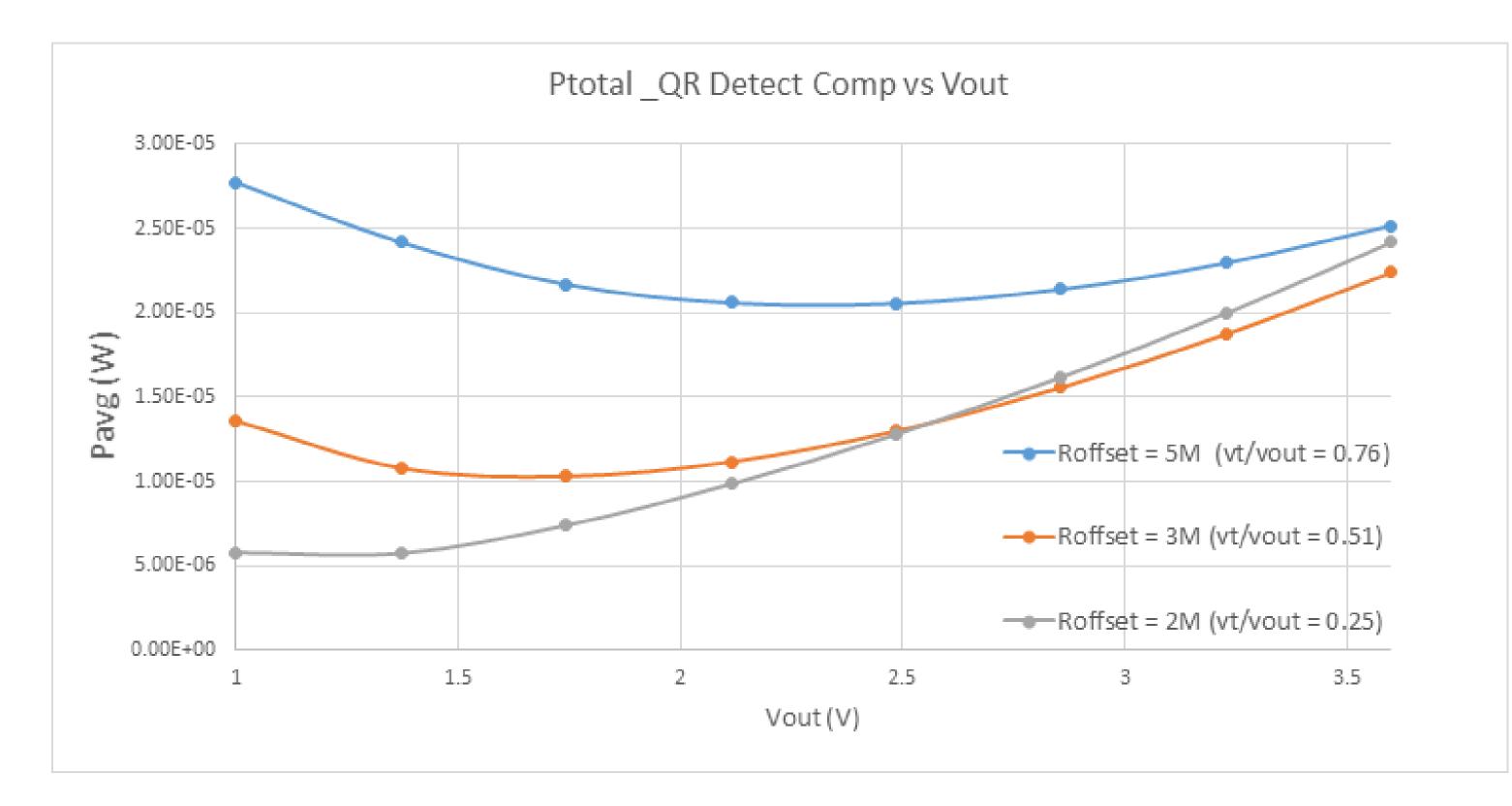

Quasi Resonant (QR) Switching achieves Zero Voltage Switching (ZVS) on Boost Switch or Buck Control Switch

### Quasi-Resonance Switching for (partial) ZVS

- Resonantly ring down voltage on Switch Node parasitic capacitance, C<sub>SN</sub>, (after S2 body diode recovers)

- Recover this into source

- Enables ZVS for lower loss

- Enables higher switching frequency, smaller size/cost

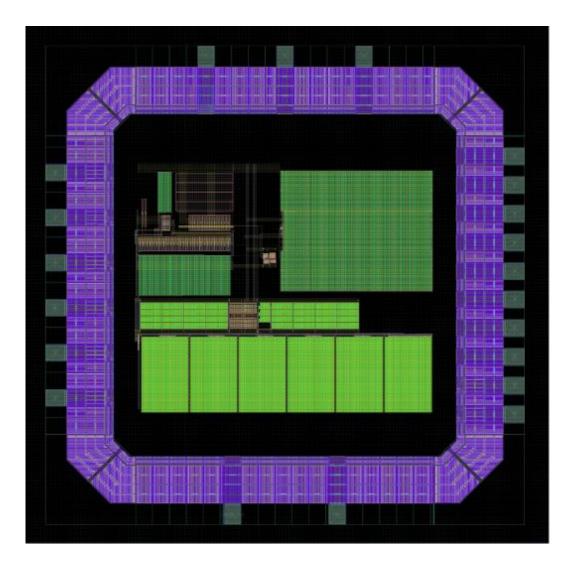

#### IC Process & Development Status

- Process: XFAB 180nm

- Automotive, Medical and -40C-175C

- Power, NVM & SOI options

- High Res Poly

- 125Kgates/mm<sup>2</sup>

- Low Sp.Ron Devices

- 10V 200V SuperJunction DMOS

- 3 Test Chips @ Top Level Schematic

- COLD START/ BIAS ALIVE Layout & DRC Clean

- POWER PATH & DRIVERS Top Level Sims ii.

- Full Chip *excluding* advanced outer control loops (hysteretic only) iii.

- Synthesised Verilog & Top Level Sims

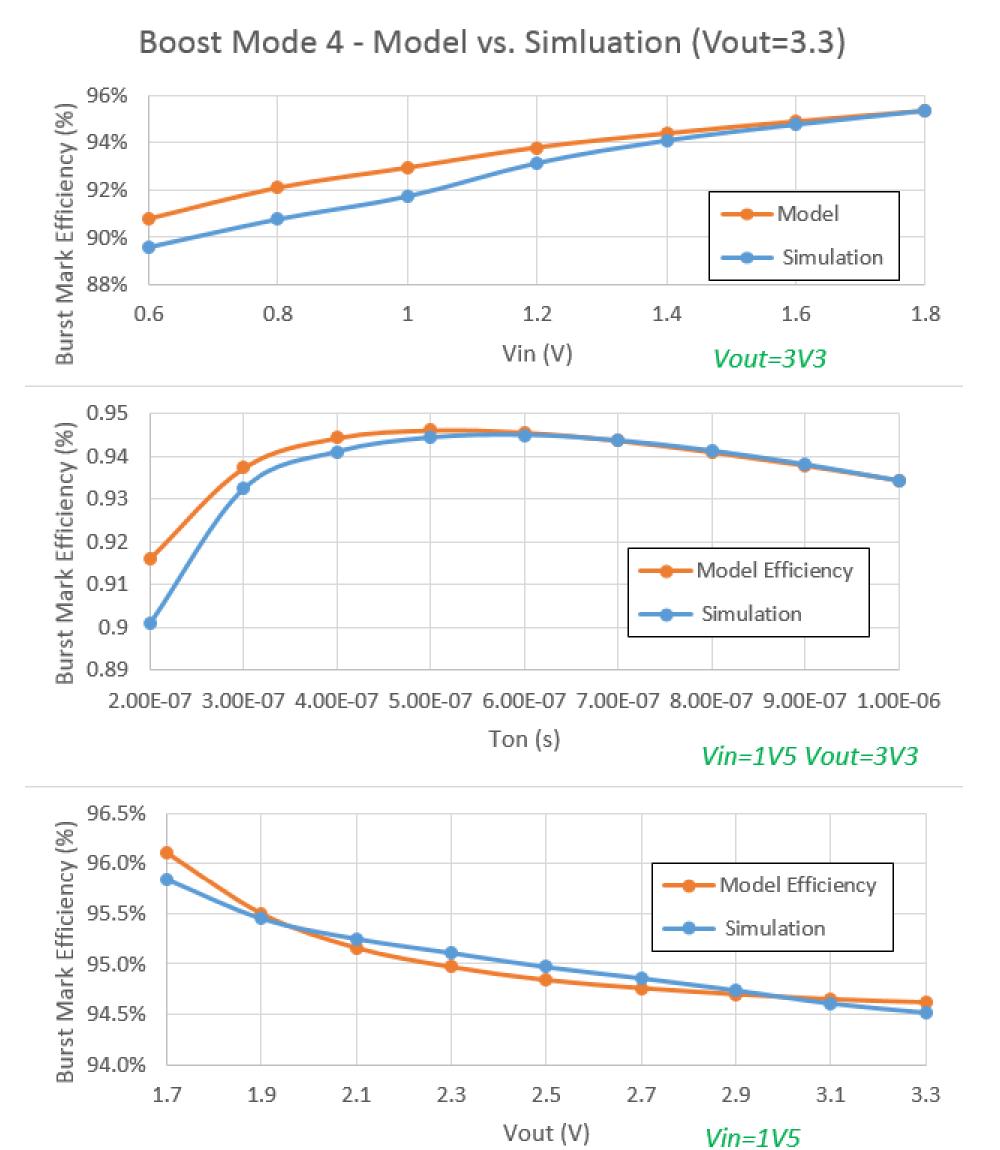

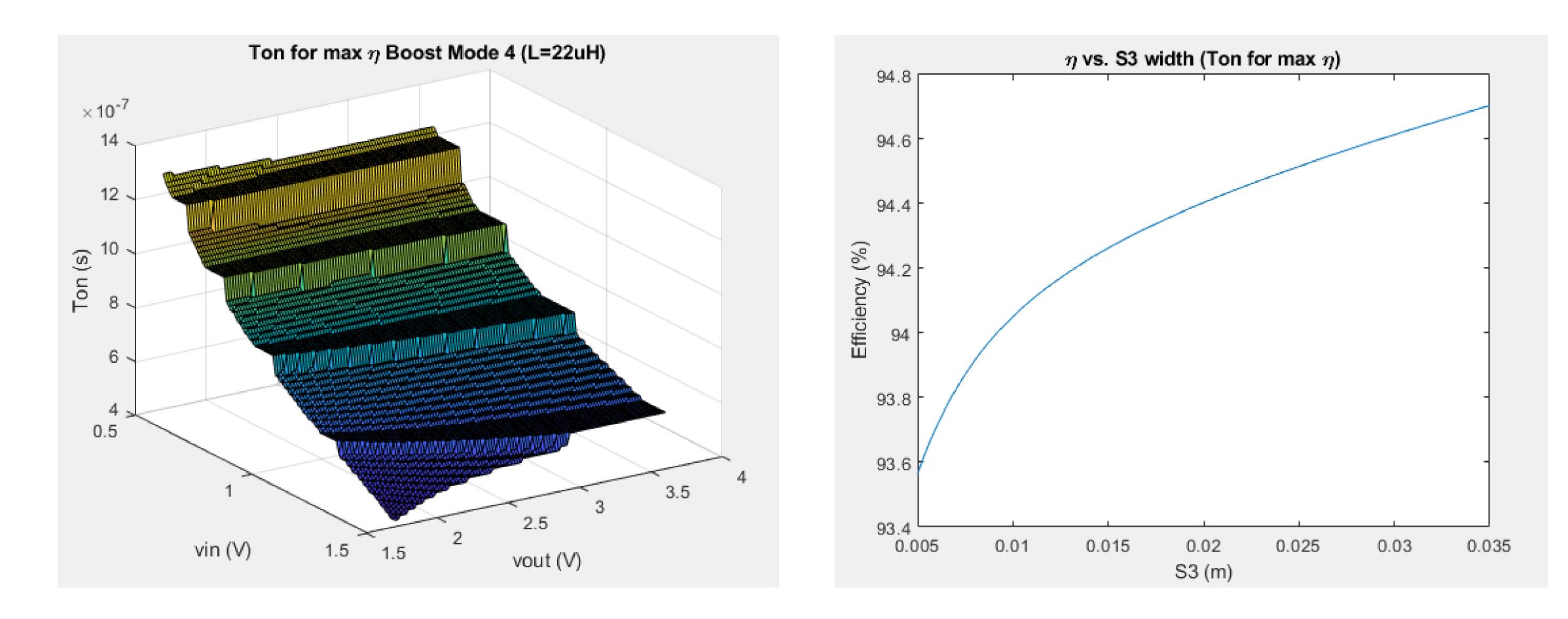

- MATLAB based *PMIC System* **Design Space Exploration**

- Complete MATLAB models match top level Cadence Simulations

# **XFAB**

0.18 Micron Modular **Trench Isolated SOI CMOS** Technology

#### Mischief Platform IC

- Cin=1uF+, Cout=10uF+, L=22uH

- SPI

- Power Path 0.1mm<sup>2</sup>

- Vin\_DC= 0.05 4V5

- Vin\_AC=50V RMS (capable)

- Vout = 1V 4V5

- 1uW 50mW

- $I_Q = 200 \text{ nW}$  (Quiescent Power)

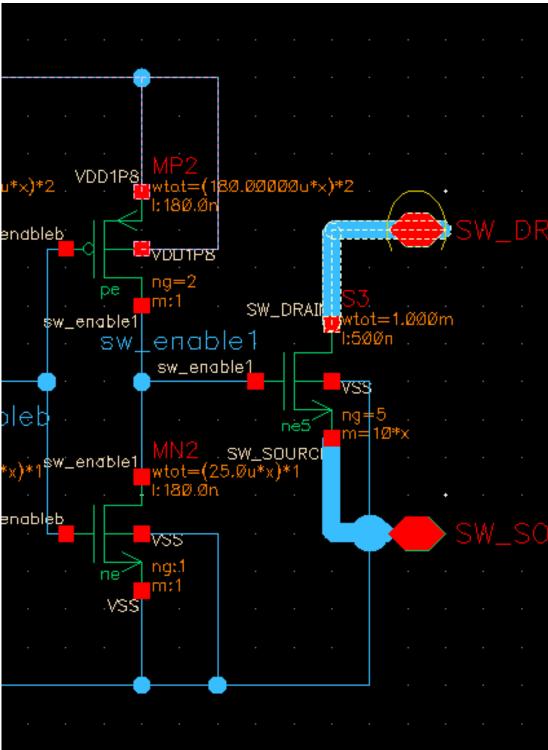

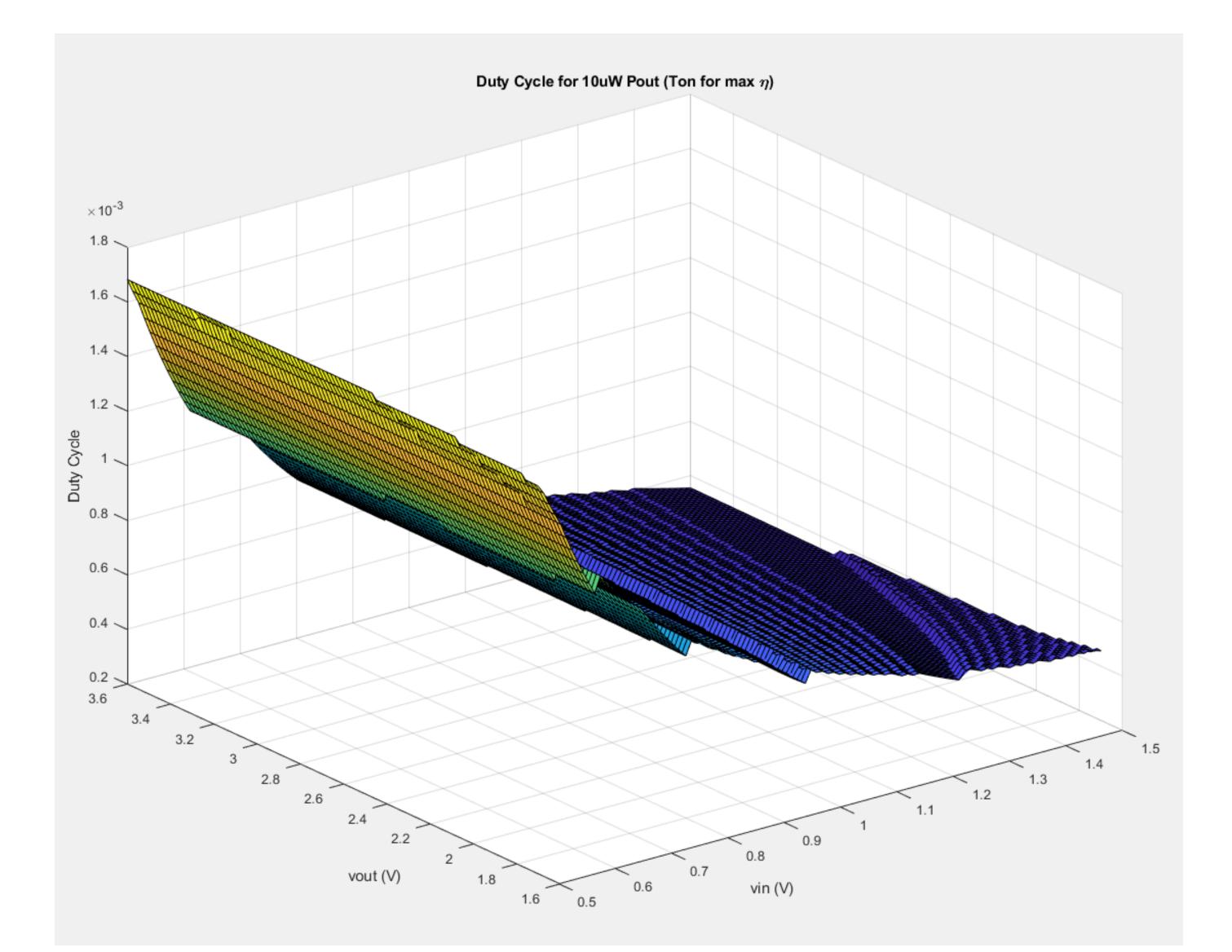

#### 4-Switch Buck-Boost Converter (Non Inverting) – Design Process

- Operating in Boost or Buck Mode More efficient than Buck-Boost Mode - or time interleaved

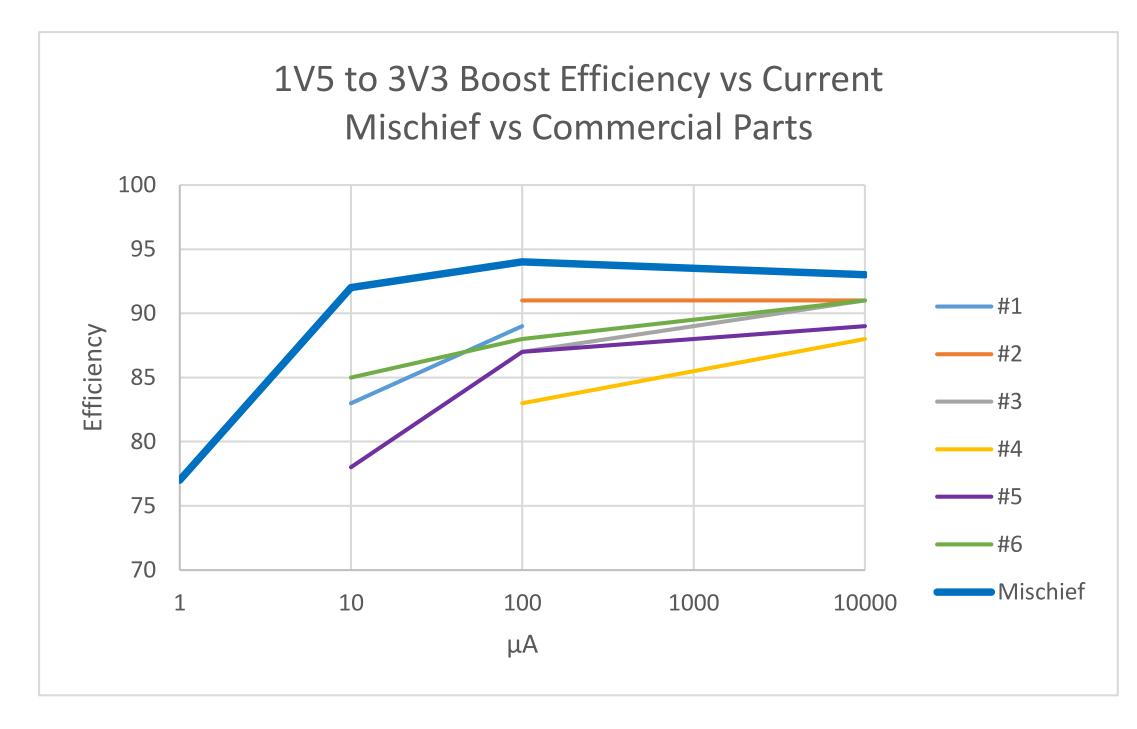

- "Typical Application" of 1V5 to 3V3 chosen for Boost Resonant Ring will give ZVS on S3

- Initial Switch Resistances chosen for Conduction Loss ~ 3%

- Analytical Models and Cadence used to find initial  $T_{ON}$  for maximum efficiency  $\{1V5, 3V3, 22\mu\text{H inductor}\}\$

- Cadence Parametric Sweep based *Design Space Exploration* by adjusting W (R<sub>DS on</sub>) for all Switches and Drivers to further increase efficiency.

| AIN   |    |   |

|-------|----|---|

| - TIN |    |   |

|       |    |   |

|       |    |   |

|       |    |   |

|       |    | - |

|       |    |   |

|       |    | - |

|       |    |   |

|       |    |   |

|       |    |   |

|       |    | • |

|       |    |   |

|       |    | • |

|       |    |   |

|       |    | • |

| u in  |    |   |

| UR    | CE | • |

|       |    |   |

|       |    | • |

|       |    |   |

|       |    | · |

|       |    |   |

|       |    | • |

|       |    |   |

|       |    | • |

|       |    |   |

|       |    | • |

|       |    |   |

#### MATLAB Modelling versus Cadence Top Level Simulations

Free running Waveforms generated by asynchronous digital state machines controlling event triggered analog latches

#### Design Process:

Analytically determine optimum T<sub>ON</sub> Cadence Parametric Sweeps on all power path components to maximise η%

# 5x10<sup>4</sup> Dynamic Range in Pout with Ton set for maximum efficiency Po $\propto f_{\text{BURST}}$

1.5

- Extend Ton or switch in parallel switches for larger dynamic range

- 10uF Cout => Vout Ripple ~0.25%

- D<sub>BURST</sub> =0.0003 @ 10uW

- DCM (QR), ZCS, ZVS

#### Digital Assisted Analog Configuring: Comparator Speed and Thresholds

- Vin ~ (Vout + Vrectifier) => low di/dt => long regions passing through HSLT or QR COMP transitions

- Separating comparator thresholds by configuration gives a 3X benefit in block consumption

- Almost all low power circuits have a configurability benefit

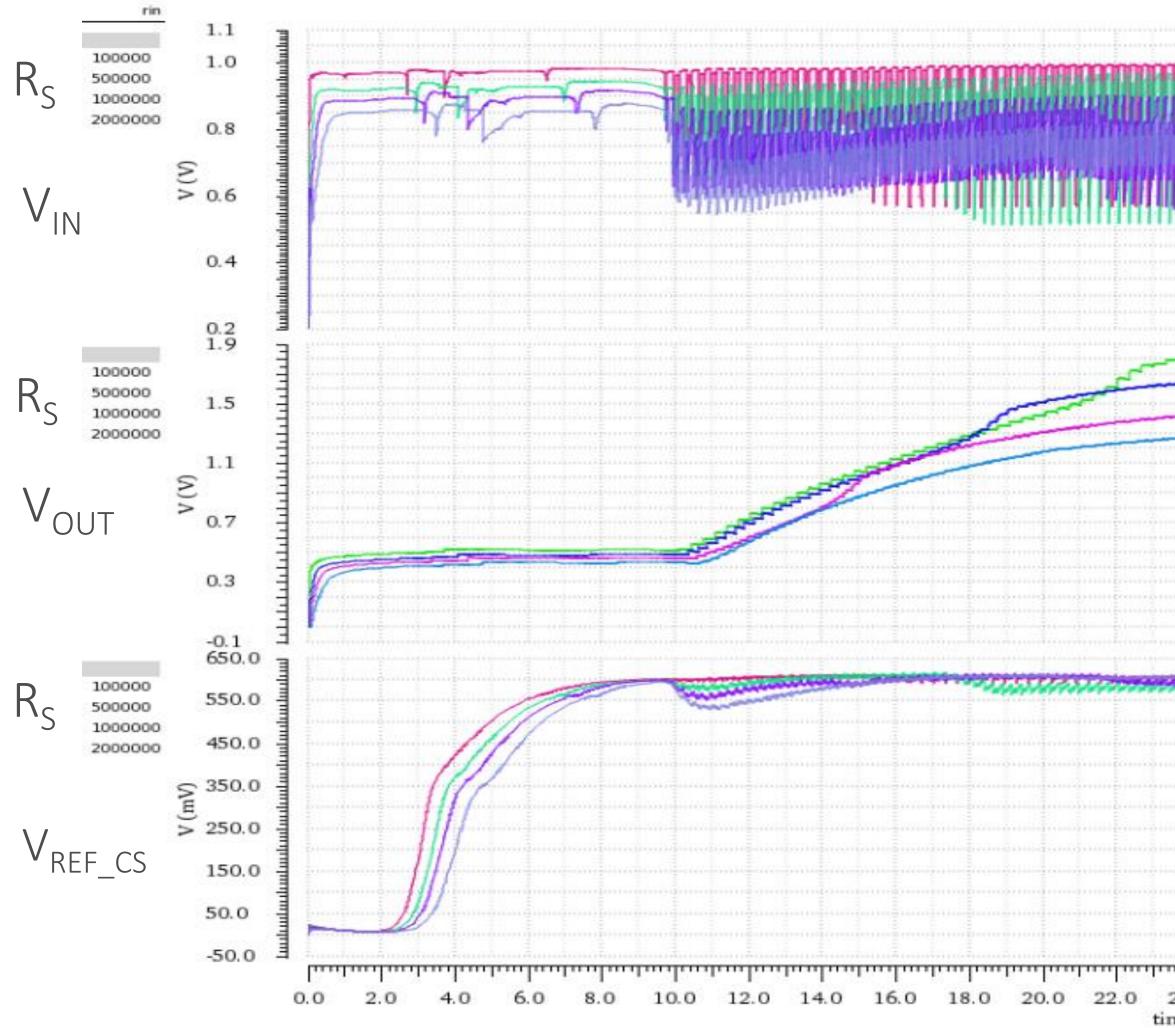

### Cold Start Block: Start-Up with Vin=1V, $R_{SOURCE}$ 100k $\Omega$ – 2M $\Omega$

|         | imm    | mun       | umu            |                     | - New       | TANKA          | URITUR   |                                                     | Info     | AL                                    | H           |

|---------|--------|-----------|----------------|---------------------|-------------|----------------|----------|-----------------------------------------------------|----------|---------------------------------------|-------------|

| ųυ      | RUDA   | 1001      | ЩЩ             | U 11.               |             |                | UPRIO    | T DIN T                                             | aug.     | <b>bho</b> r                          | n.          |

| ilit:   |        | with      | ni di          | in li               |             |                |          |                                                     |          |                                       |             |

|         |        |           |                |                     |             |                |          |                                                     |          | 114                                   |             |

| 11      |        | min       | mini           | min                 | IIIIIIII    |                |          | INUU                                                | 111 11   | i mu                                  | 11          |

|         |        |           |                |                     |             |                | 1        | 1121112                                             | 11210012 |                                       | -           |

|         |        |           |                |                     |             |                |          |                                                     |          | n in the second                       | 1.<br>L     |

|         |        |           |                | H                   |             |                |          |                                                     |          | 11                                    |             |

|         |        |           |                |                     |             |                |          |                                                     |          |                                       | ÷.          |

|         | 6      | -         | -              |                     |             |                |          |                                                     |          | -                                     | -           |

|         |        | 1         |                |                     |             |                |          |                                                     |          |                                       | 0.10        |

|         | 1      |           |                | ilan in Errei       | Territory   |                |          |                                                     |          |                                       | -           |

|         |        |           |                | 1)E<br>1]E          |             |                |          |                                                     |          |                                       |             |

|         |        |           |                |                     |             |                |          |                                                     |          | · · · · · · · · · · · · · · · · · · · | 101         |

|         | į      |           |                |                     | 1           |                | 10       | 11                                                  |          |                                       | Ť.          |

|         | 1      |           | 1              |                     | 1           |                |          | The second second                                   |          |                                       | Ť           |

|         | ****** |           |                | 11111100<br>1111100 |             |                |          |                                                     |          | HIIIIII                               |             |

| ******* | ÷)     |           |                |                     |             |                |          |                                                     |          | · · · · · · · · · · · · · · · · · · · |             |

|         |        |           |                |                     |             |                |          |                                                     |          |                                       | 1           |

| and     | mun    |           | ru da          |                     | 11-57       | maine          | many     | matrice                                             | With a   | -                                     |             |

|         | milia  |           | and the second | unnus               | manna       | annan          | unner    | anna                                                |          |                                       |             |

|         |        |           |                |                     |             |                |          |                                                     |          |                                       |             |

| ******  |        | 11131-111 |                |                     |             | i de receijose | Himmedia | 111111115                                           |          | in the first                          | nā.         |

|         | 6      |           |                | (0⊕100)<br>         | 1011000-000 |                |          |                                                     |          |                                       | 1           |

|         | ğundu. |           |                | inn in              |             |                | uine le  | u na seconda se | n finn f | kimpon                                |             |

|         |        |           |                |                     |             |                |          |                                                     |          |                                       |             |

|         |        |           |                |                     |             |                |          |                                                     |          |                                       |             |

|         |        |           |                |                     |             |                |          |                                                     |          |                                       |             |

|         |        |           |                |                     |             |                |          |                                                     |          |                                       |             |

| uluu    | վուսես | արաղ      | miliun         | h                   | աստ         | աստանու        |          | ահասհ                                               |          | mhu                                   | <b>'</b> T' |

2-16nA | Bias Gen 1kHz Osc Charge Pump Fractional BG DAC Comparator Total Current = ~60nA V<sub>START</sub> ~0.45V

#### Power Path Efficiency @ $1\mu$ W = 95%

#### Burst Duty Cycle (independent of pulses per burst)

- Po = 10 uW

- D =1 in 1000

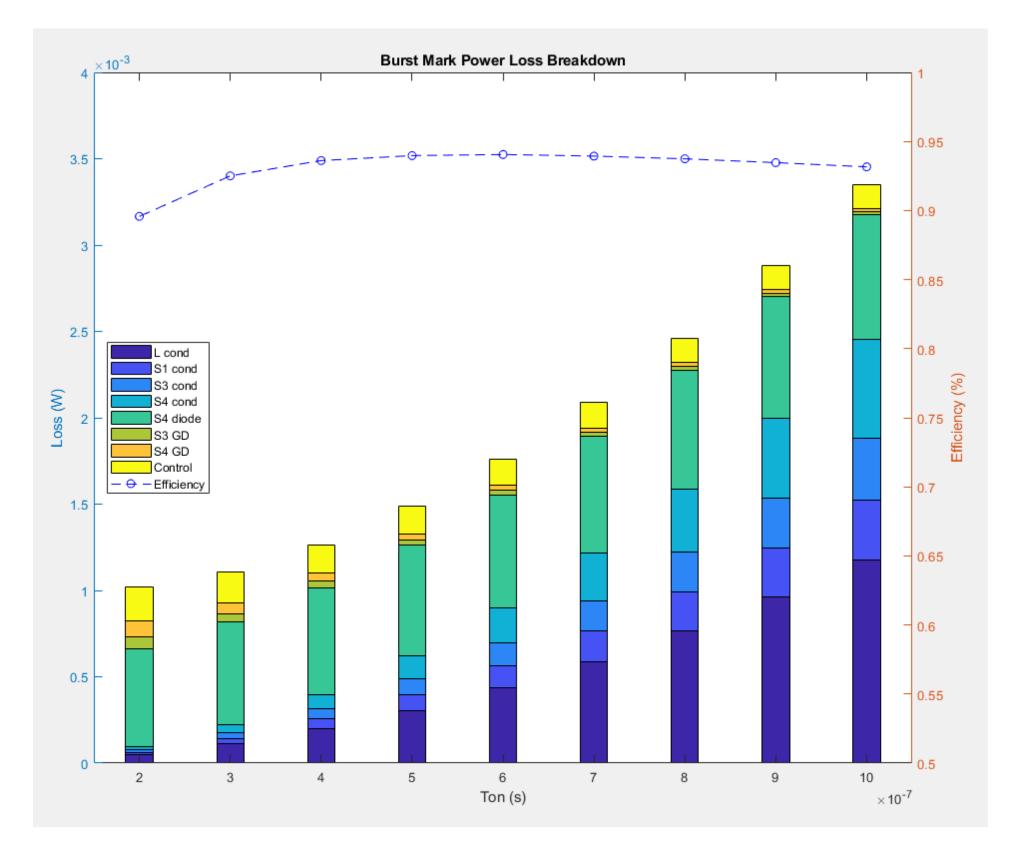

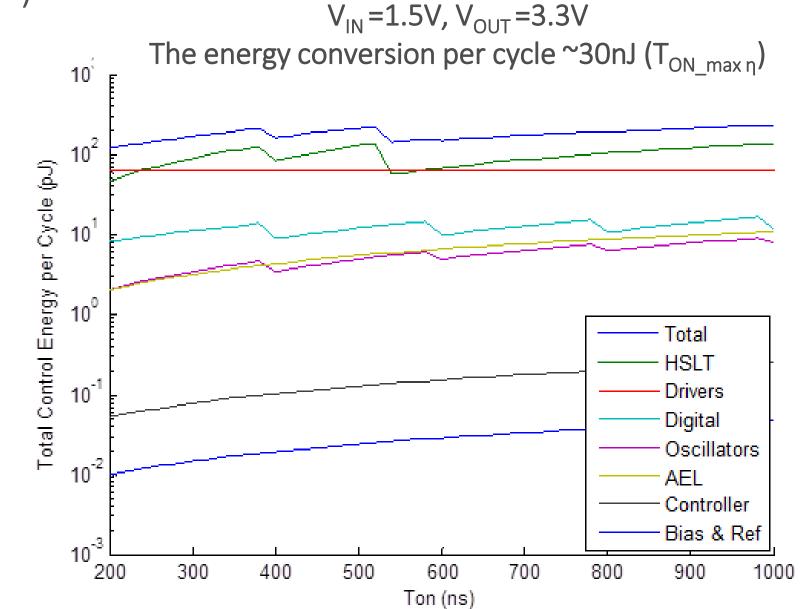

#### 10uW, 1V5-3V3, 22uH Burst Mark Power & Efficiency vs Ton

- S1-S4 Switching Loss is very low

- S4 Body Diode Conduction could be designed out

- There is opportunity to remove the large inductor

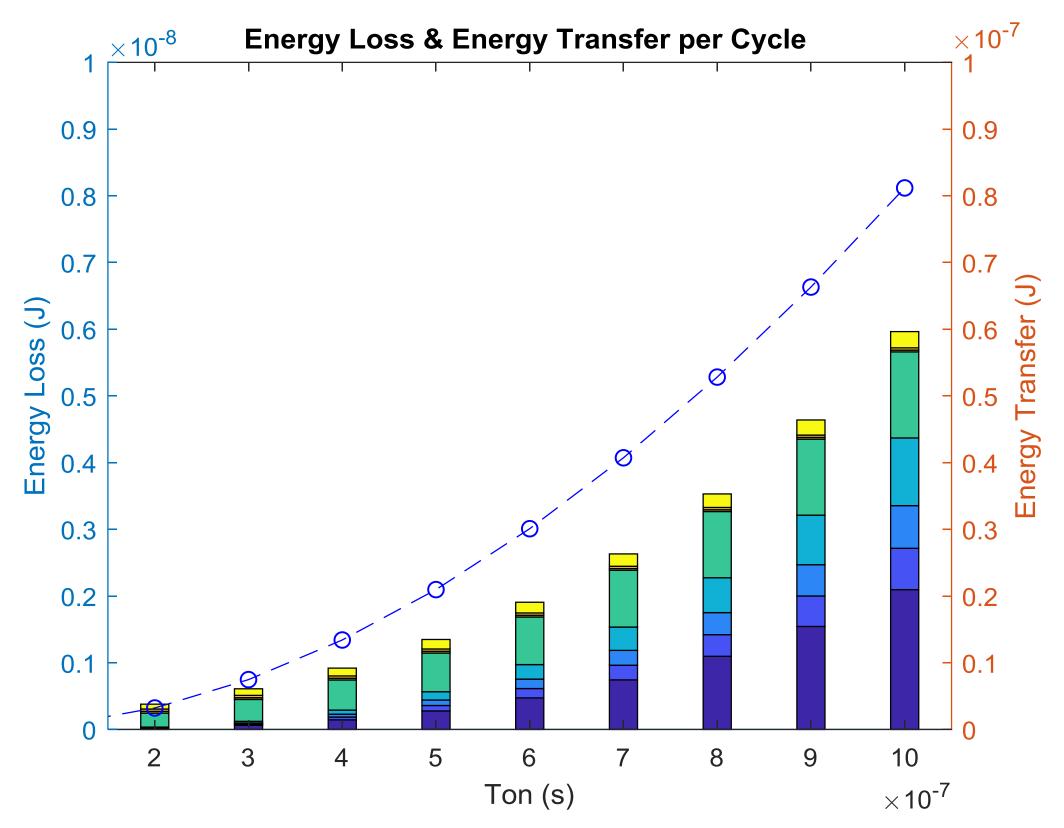

#### 10uW, 1V5-3V3, 22uH Energy Loss and Energy Transfer per cycle vs Ton

#### Sample IP Blocks

- Mixed signal innovative architecture

- Extra low input voltage operation

- Asynchronous PWM Modes Generation

- Ultra efficient power path, gate drives and level shifters design

- 20nA Voltage Comparator

- 10ns Current Input Comparator

- 10ns High Side Voltage low voltage threshold Comparator

- Starved Inverter Ring Oscillators

- <100nA Cold Start: Oscillator/Charge Pump/Fractional reference system

- SPI Master Configurable Mixed Signal (external Serial EEPROM)

- High speed analog event detect latches (power cycleable)

- Variety of Digital-to-time converters (DTC)

- Ultra Low Energy ADC Systems

. . . . . . . . . . . . . .

Asynchronous master control state machines

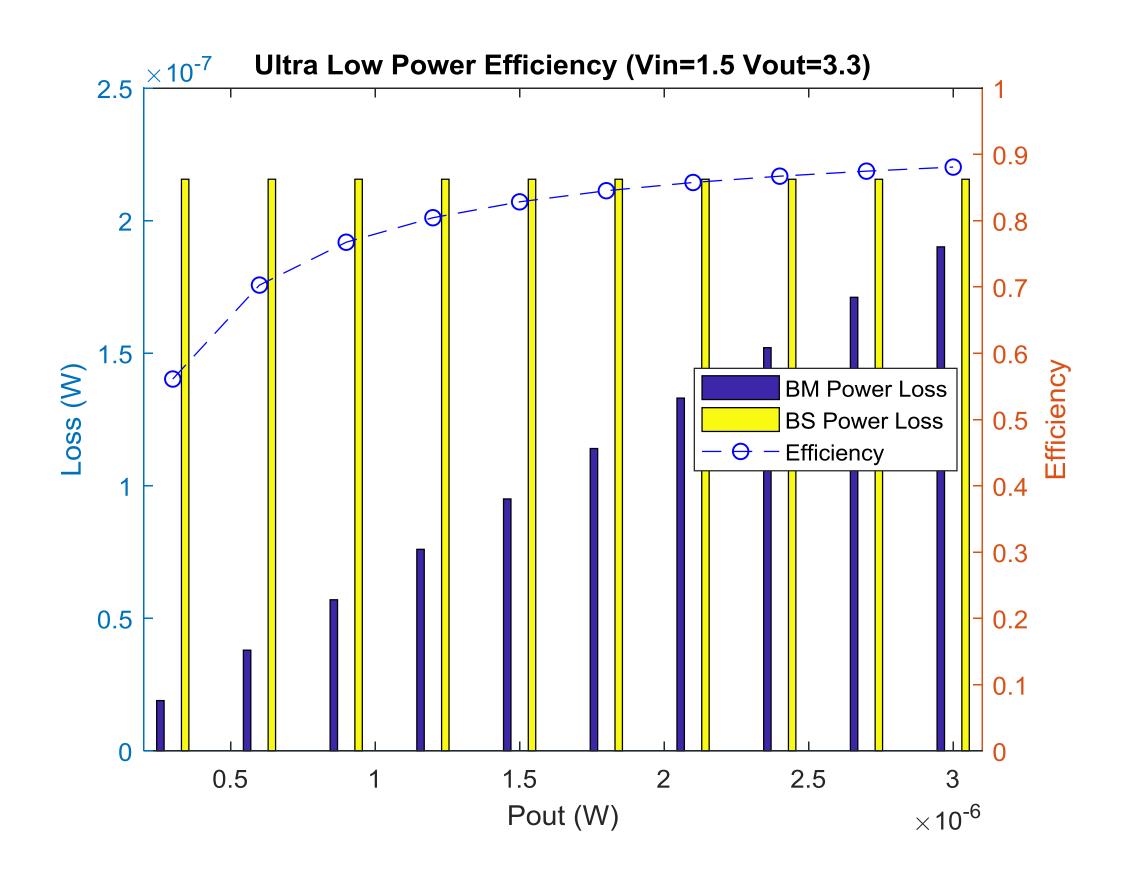

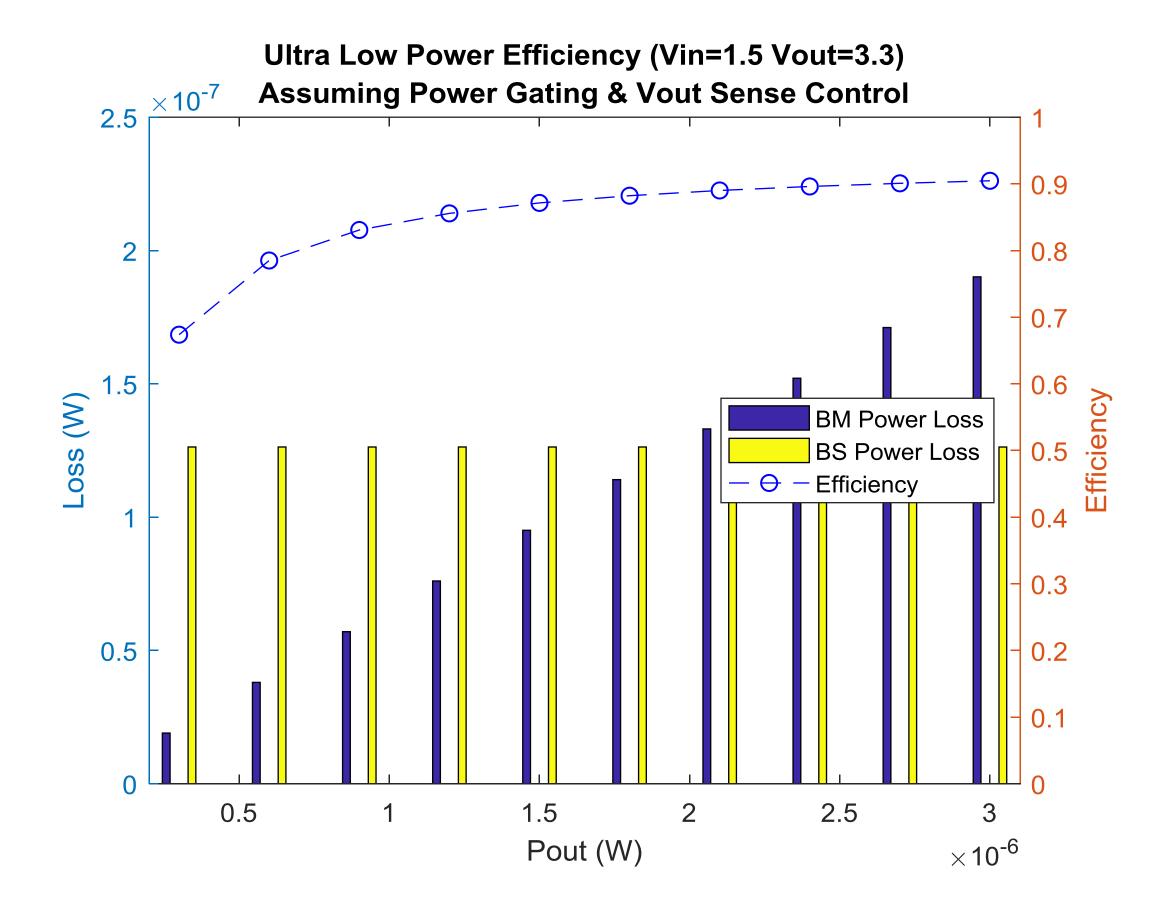

#### 4 Switch QR Non Inverting Buck-Boost Power Path for 95% efficiency from 1uW to 10mW

#### 80+% efficiency @ 1μW

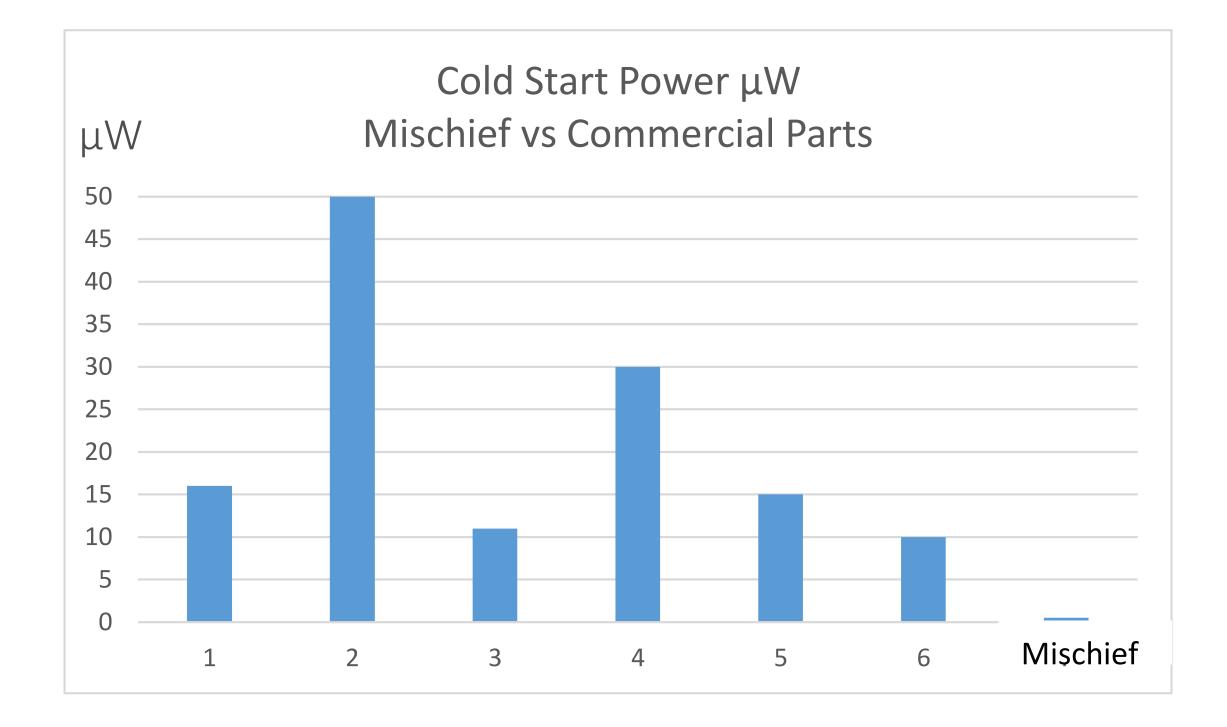

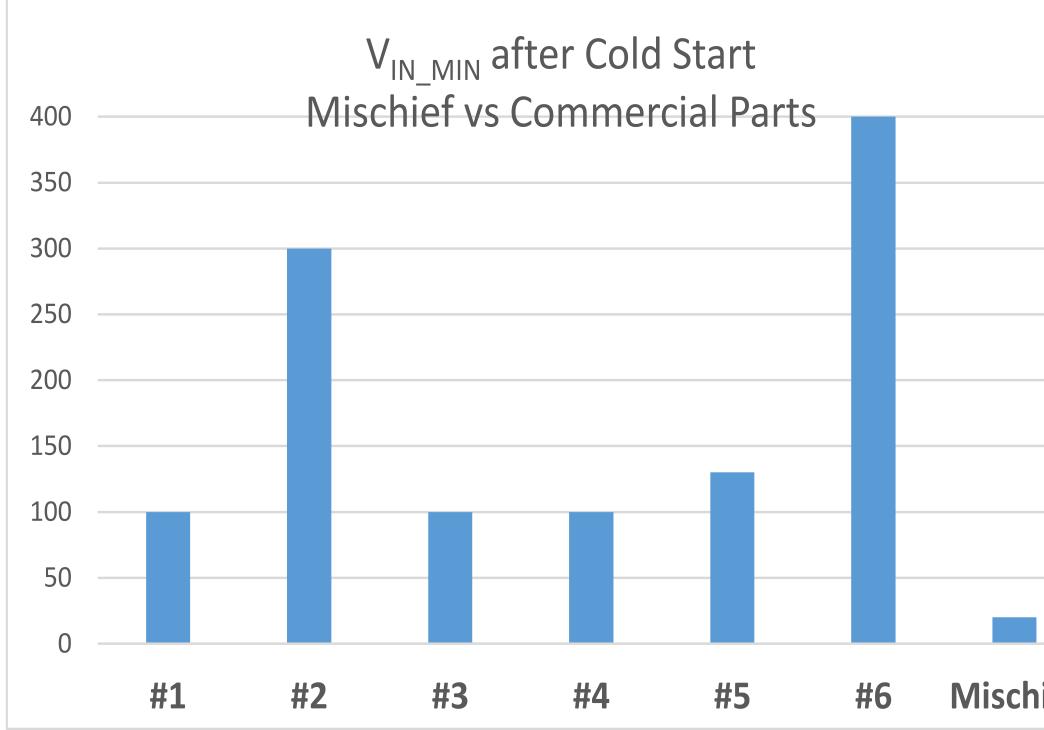

### Mischief vs Commercially Available Parts (2017)

Only one part surveyed has buck-boost capability None have advanced digital configurability (SPI)

Mischief based on Top Level Schematic Sims (not LVS)

Part nos ADP5090, MB39C831, AEM10940, SPV1050, BQ25504, MAX17220

#### Mischief versus Commercially Available parts

Low V<sub>IN</sub> operation (after Cold Start)

| hief |  |

|------|--|

|      |  |

|      |  |

|      |  |

| Marketplace EH<br>PMIC | SPI/I2C<br>Interface with<br>Host WSN<br>Controller | Topology                   | Low Output<br>Voltages |  |

|------------------------|-----------------------------------------------------|----------------------------|------------------------|--|

|                        |                                                     |                            |                        |  |

| #1                     | No                                                  | Boost                      | No                     |  |

| #2                     | No                                                  | Boost                      | No (3V+)               |  |

| #3                     | No                                                  | Cascade Boost,<br>Buck+LDO | Yes                    |  |

| #1                     |                                                     | Boost, Buck-               |                        |  |

| #4                     | No                                                  | Boost, LDO                 | Yes                    |  |

| #5                     | No                                                  | Boost                      | No (2V+)               |  |

|                        |                                                     |                            |                        |  |

| #6                     | No                                                  | Boost                      | No                     |  |

| Mischief               | Yes                                                 | Buck-Boost                 | Yes (1V+)              |  |

#### Control & Drive Efficiency vs Research

(considering 100 X Po difference between these designs) IBM, MIT Research ISSCC'17 65nm

Overall Control Energy Loss for 240 pW Quiescent (0.8mW max) Buck Converter 2V-0.8V, 47uH (65nm CMOS)

#### Energy Out ÷ (Control+Drive) Energy per Cycle => $(\eta_{CONTROL}) = 95.6\%$

A Buck Converter with 240pW Quiescent Power, 92% Peak Efficiency and a 2x10<sup>6</sup> Dynamic Range, Arun Paidimarri, Anantha P. Chandrakasan, ISSCC'17

#### Tyndall MCCI, Mischief '18 180nm

Overall Control Energy Loss for 200 nW Quiescent (27mW) @T<sub>ON max n</sub>) Buck-Boost Converter 1V5-3V3, 22uH (180nm CMOS)

Energy Out ÷ (Control+Drive) Energy per Cycle =>  $(\eta_{CONTROL}) = 98.83\% (@T_{ON_{max \eta}} = 600ns (max. \eta)$

S3 GD = 27pJ, S4 GD=34pJ @ Ton = 600ns for 1V5 to 3V3, 1kHz/1ms Burst Space assumed = 200pJ

#### Conclusions

Advanced real time system optimisation is feasible for highly featured 350nW+ designs

- Advanced digital modulators and control are applicable, next step add ULE ADC Digital filtering and outer loops may be implemented by node host controller

- Power System Design selects T<sub>ON</sub> for maximum efficiency at all points Host -> SPI -> Config Benefit

- Extensive Matlab modelling and top level Cadence simulation match-up

- Our Control and Modulator Energy Efficiency is very high

- Our Quiescent Current could be substantially reduced by HSLT redesign, switched senses and power gating

- Our architecture is future proofed for considerably higher frequencies

- Our architecture is applicable for maximising energy transduction and efficiency for a wide range of emerging MEMs and Micro Scale Systems

- IP for IoT Node ASICs, SoCs

#### Team

- James McCarthy

- Tim Daly

- Gerry McGlinchey

- Ivan O'Connell, Séamus O'Driscoll

# Thank You

Cilia Cilia

Dj

......

0:00

CER