#### 180nm CMOS Buck-Boost Converter with Mixed Signal Control for 1uW to **100mW Power Conversion**

#### 6<sup>th</sup> April 2022

Séamus O'Driscoll

seamus.odriscoll@tyndall.ie

<u>www.mcci.ie</u>; <u>www.tyndall.ie</u>

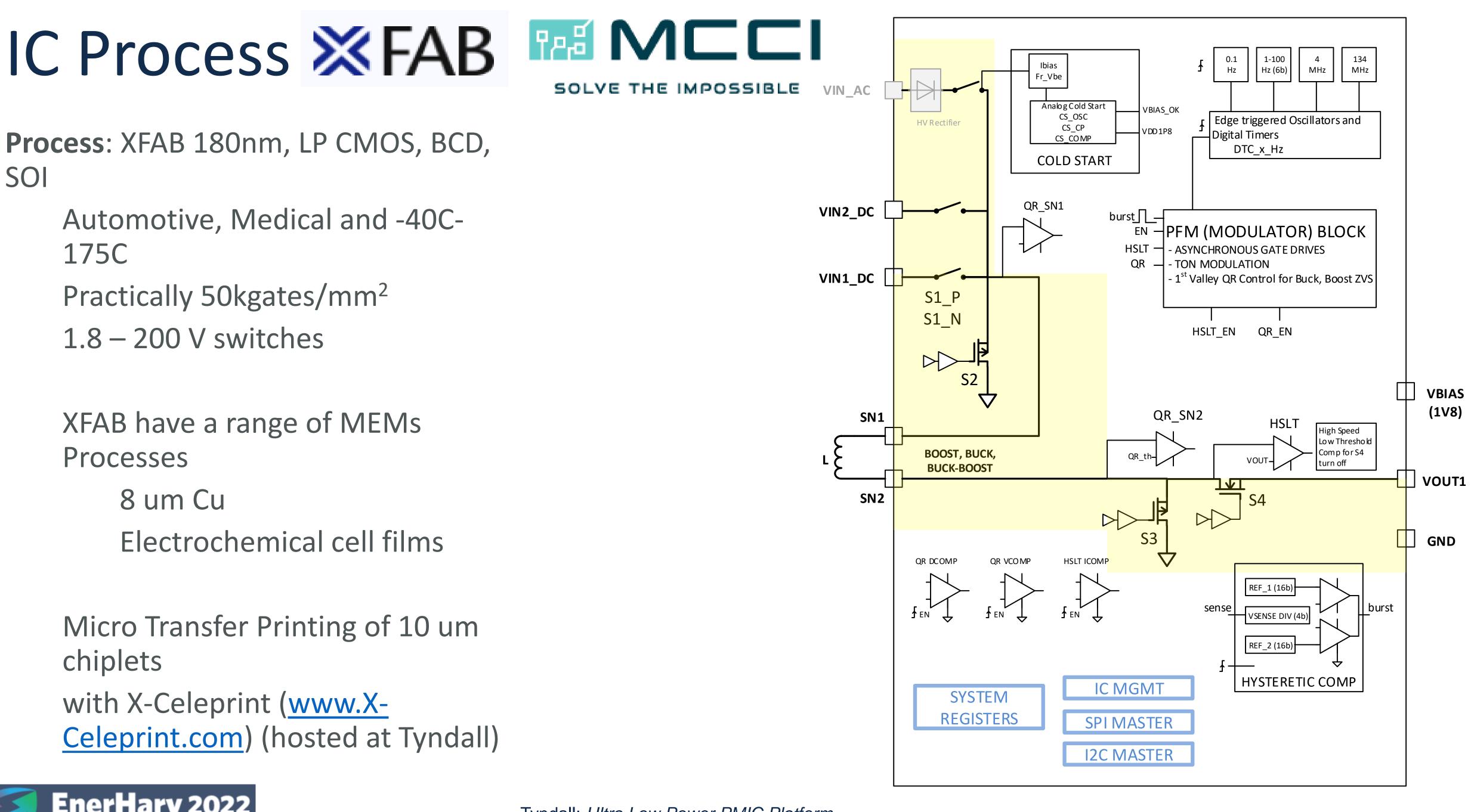

SOLVE THE IMPOSSIBLE

Rialtas

of Ireland

Tionscadal Éireann Project Ireland na hÉireann Government 2040

**European Union** European Structural and Investment Funds

## Powering the trillion ultra low power sensor nodes

Multiple dynamic intermittent sources Large dynamic ranges in source and load powers,  $10^5 +$ **Complex Power Systems** *Power/Energy Centric* Systems; Large Variety of Variable Ambient Environments Source Power Transducer Efficacy Improvements **Power Factor Correction, Synchronous Charge Extraction Advanced Features**

Gas-Gauge, MPPT, Condition Monitoring, System Optimisation

## PLATFORM VISION

- Highest efficiency from  $< 1 \,\mu W$

- Multiple inputs, outputs and power flow directions

- DC, AC Sources from 30 mV to 100s' V

- SPI Digitally Configurable

- Flexible Architecture

- Asynchronously triggerable functionality blocks

### Solution by State Machine design -> Register Config -> + Micro Code

Support the SoC with Transducer, Storage and Load Interface

Based on the premise that energy efficient digital control is feasible for advanced features – MPPT, Energy and Condition Metrology

## Platform Approach: Power and Energy

Designing for On-State – Energy Per On state Quiescent power Optimum Energy transfer per switching cycle Energy per timed second Energy per PFM modulator cycle Energy per control sample – dynamic bandwidth, as required Energy per function

Designing for Off-State – leakage power minimisation Minimum Power during Burst Spaces Low sleep mode – with timed wake or analog event driven wake

Duty Cycling – asynchronously triggered circuits – rapid on-off - functionality on demand Dynamic Comparators, Oscillators, References, Amplifiers, ADC, DACs

Tyndall Tech Talk: Ultra Low Power Platform

July 2021

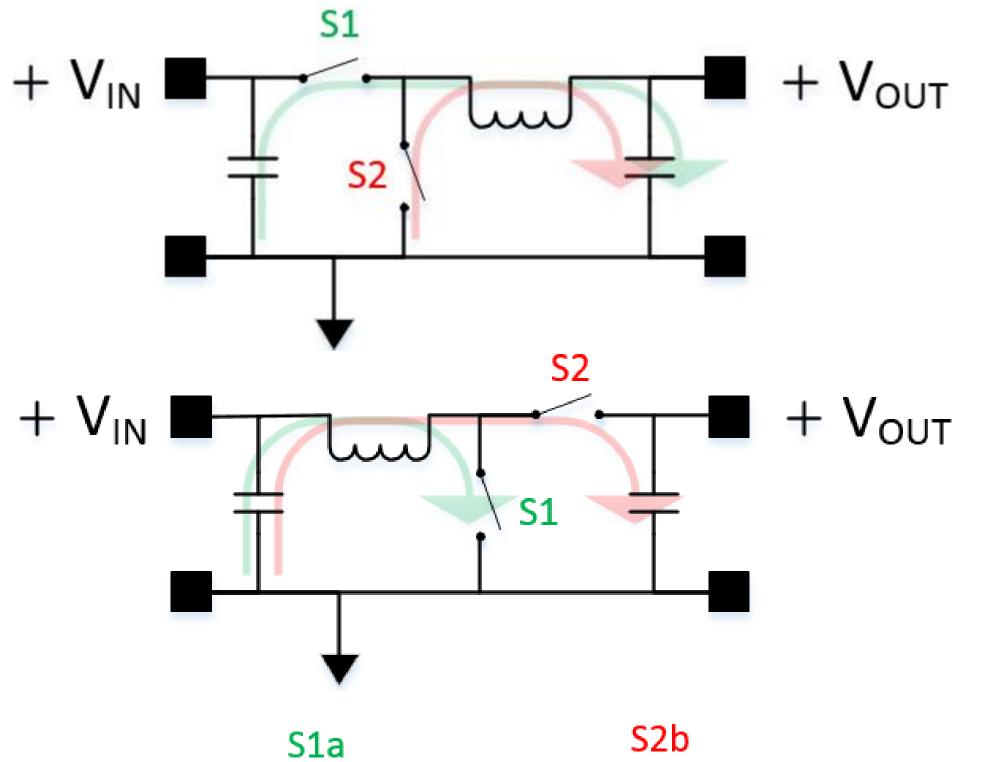

## Switch Mode Inductor Topologies

Buck  $V_{IN} > V_{OUT}$  Inductors are beautifully voltage compliant

Buck or Boost is more efficient than **Buck-Boost**

Boost  $V_{OUT} > V_{IN}$

The Buck-Boost can cater for multiple and varied interleaved sources and outputs

Inductors are large when looking for small  $\Delta i$

Parking the challenge of topology change and inductor integration

**Buck-Boost**  $V_{OUT} <,> V_{IN}$

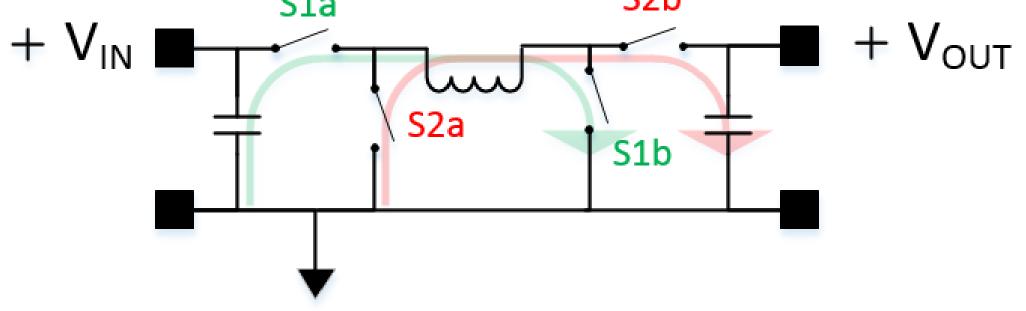

# Post Layout (PEX) Simulated Performance Syndall

PEX Simulations IC (M2a) VOUT\_HIGH\_pic /S3\_N\_IN\_di 1.5 $\Xi^{1.1}$ > 0.7 Boost Mode 1V5 to 3V 0.3 -0.11.9 PFM\_BSTSR\_TST1 modulator /S4\_P\_IN\_di 1.5  $\ge$ <sup>1.1</sup> > 0.7 0.3 -0.14.0 Waveforms for single cycle 3Vin, 22uH, /VSN2\_a io 2.8 124mA pk, ~300nJ transferred ≥ ^ 1.2 -0.4 3.5 /VOUT\_HIGH\_pio 3.3 ≥ 3.1 > 2.9 2.7 2.5 Exaggerated intervals of S4 body diode 2.0 /VIN\_pi 1.8conduction for illustration of SR  $\sum_{>1.6}^{1.6}$ 1.21.0💻 Л ОЛЯН ЦК Note the low switch node damping P 35.0 15.0& Inductor DCR set high at  $800m\Omega$  for this simulation VOUT\_HIGH\_pic P 35.0 15.0Modulator waveforms by DSM building with

DTC

Tyndall: Ultra Low Power PMIC Platform

Thu Nov 28 16:33:40 2019

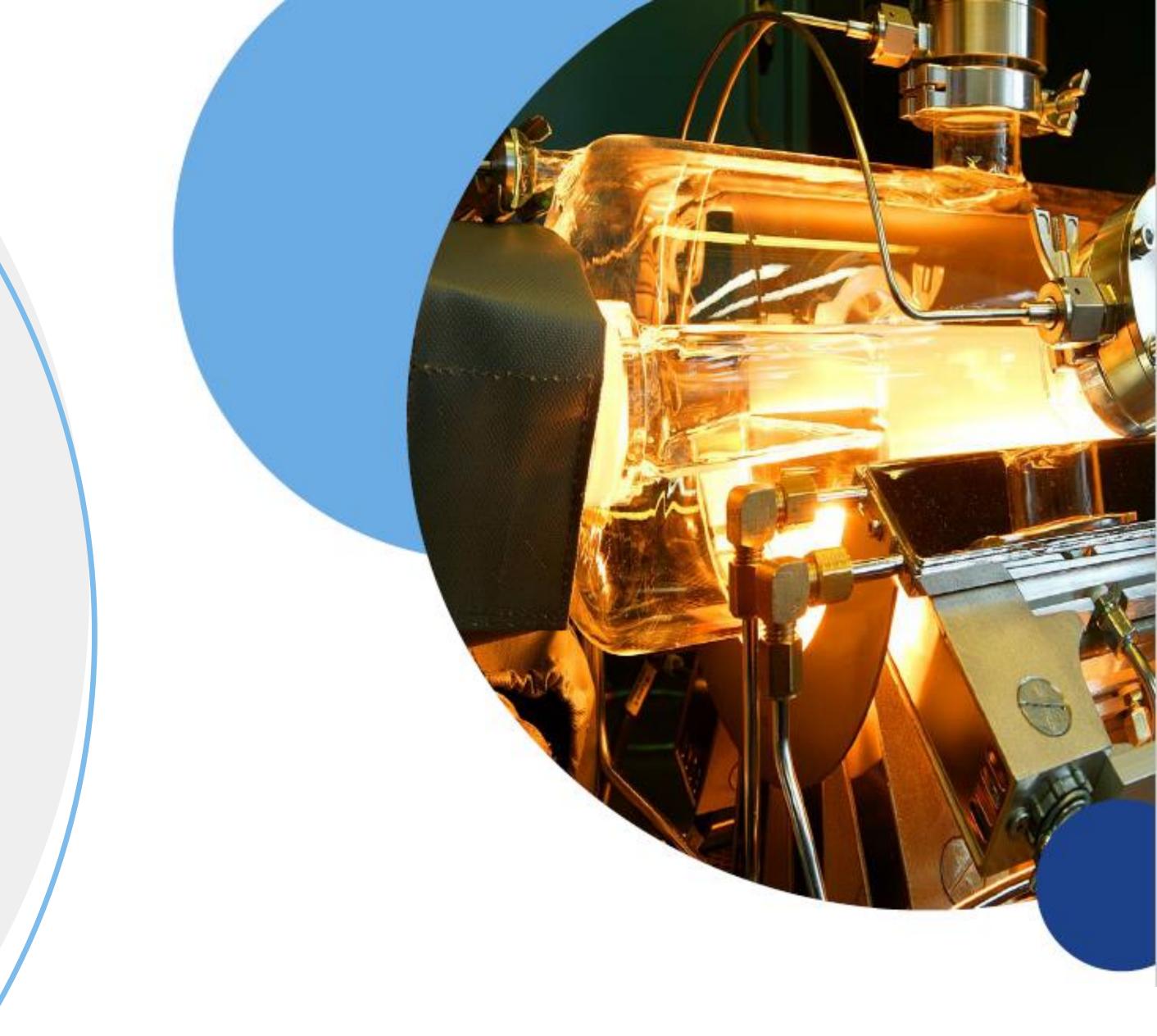

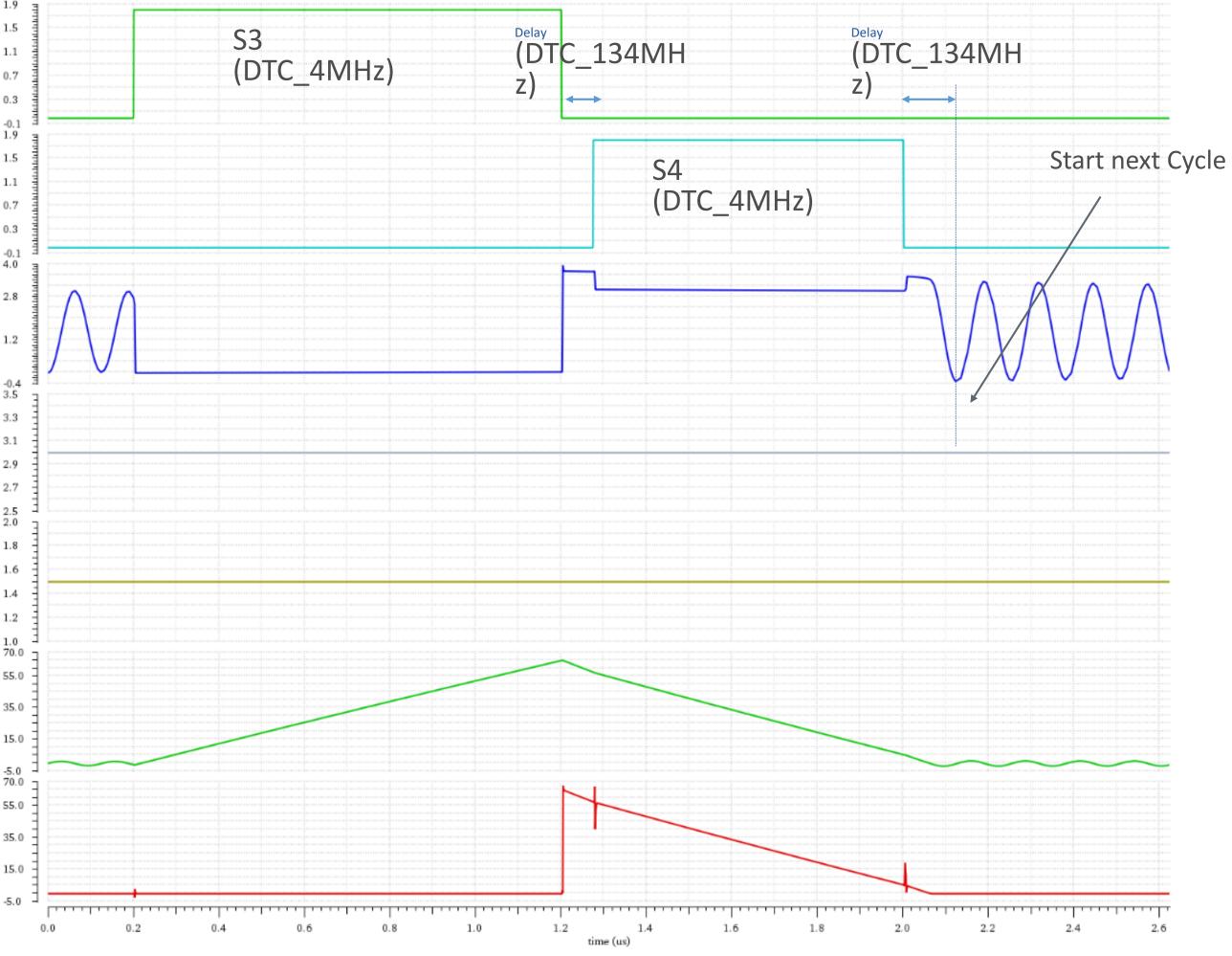

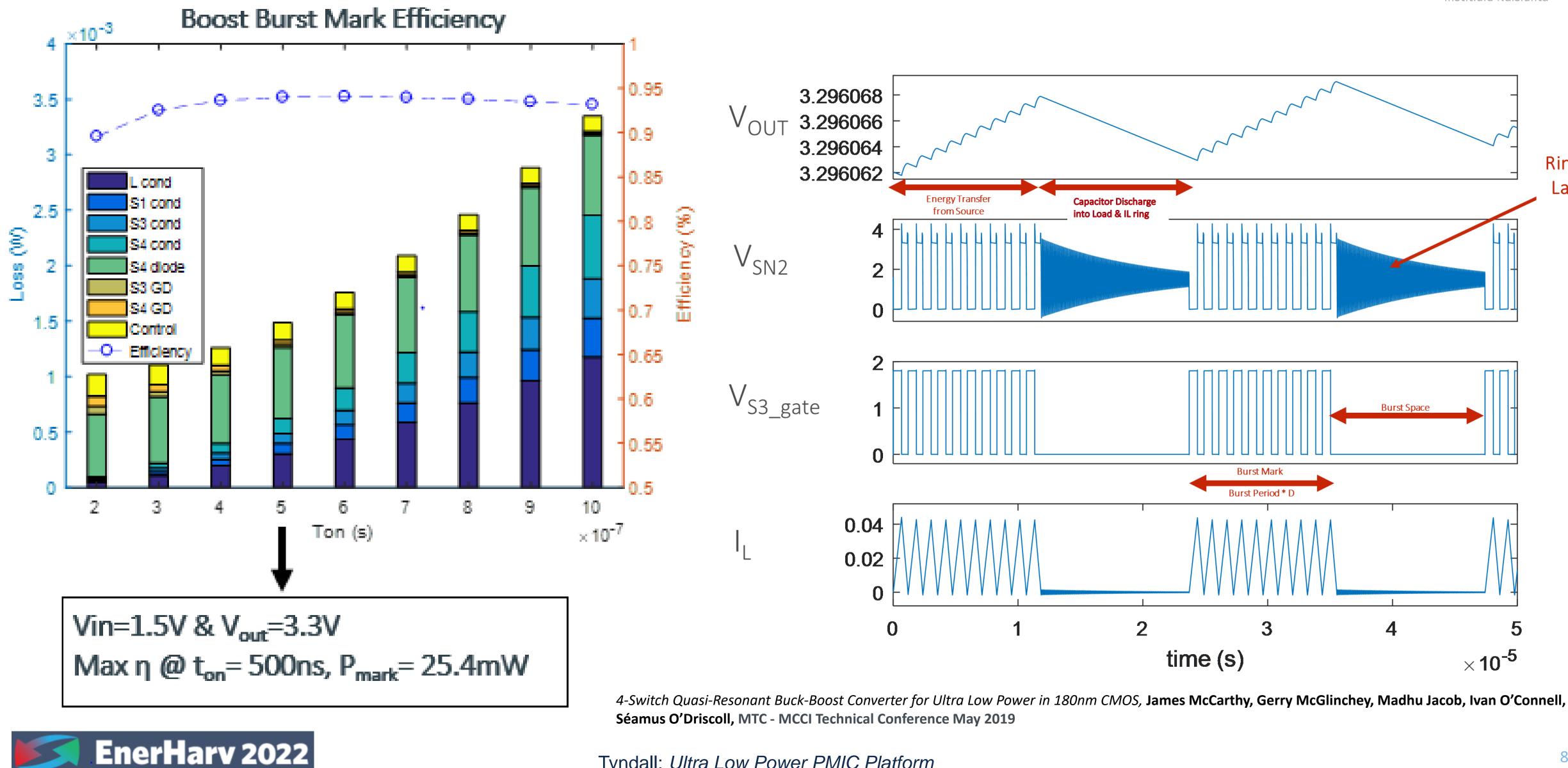

### **Optimised Per-Cycle Efficiency & Burst Mode**

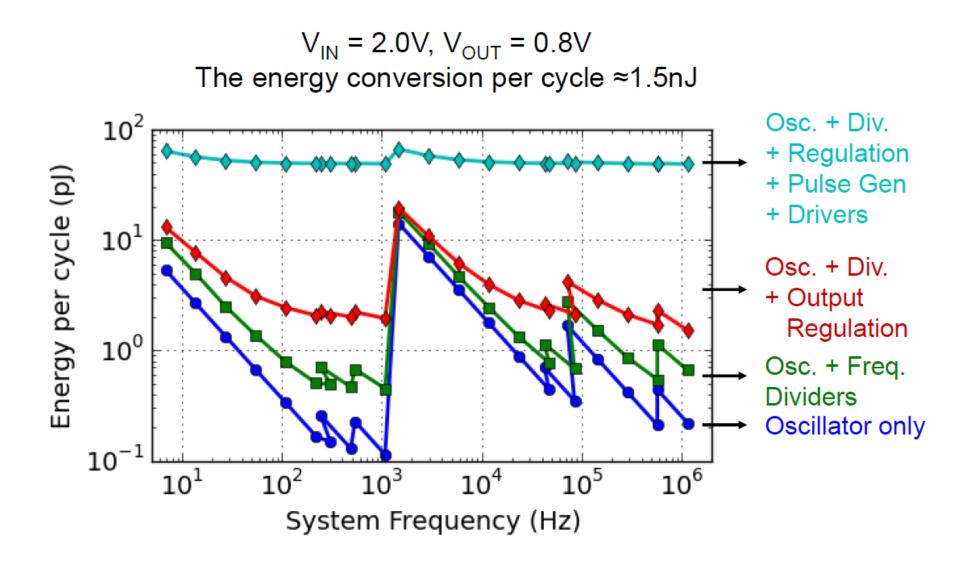

## **Control & Drive Efficiency vs Research**

(considering 100 X Po difference between these designs)

#### IBM, MIT Research ISSCC'17 65nm

Overall Control Energy Loss for 240 pW Quiescent (0.8mW) *max*) Buck Converter 2V-0.8V, 47uH (65nm CMOS)

#### Energy Out • (Control+Drive) Energy per Cycle => $(\eta_{CONTROL}) = 95.6\%$

A Buck Converter with 240pW Quiescent Power, 92% Peak Efficiency and a 2x10<sup>6</sup> Dynamic Range, Arun Paidimarri, Anantha P. Chandrakasan, ISSCC'17

#### Tyndall Tech Talk: *Ultra Low Power Platform*

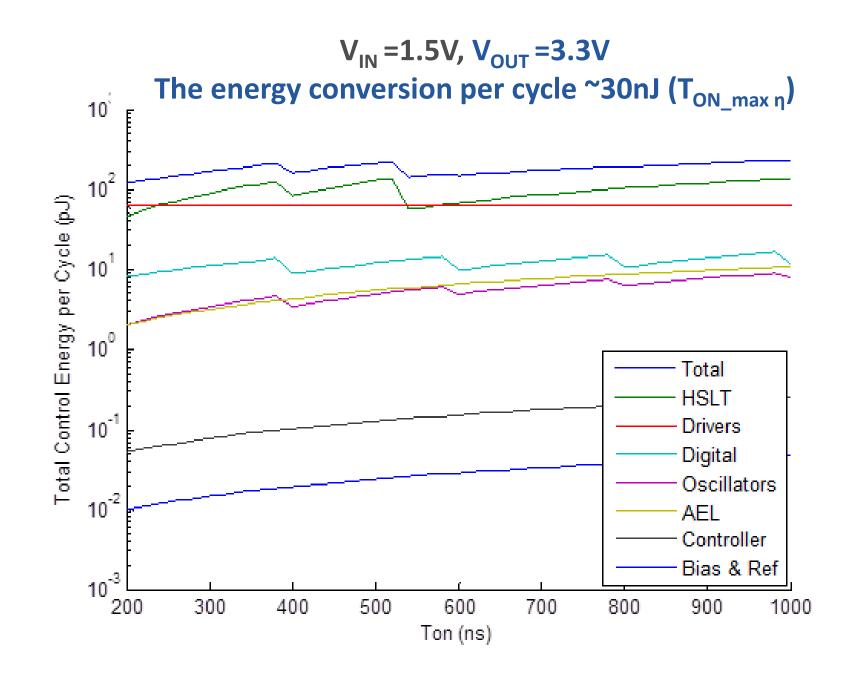

#### Tyndall MCCI, Mischief 180nm (SCH SIM)

Overall Control Energy Loss for 200 nW Quiescent (27mW @T<sub>ON max n</sub>) Buck-Boost Converter 1V5-3V3, 22uH (180nm CMOS)

Energy Out • (Control+Drive) Energy per Cycle =>  $(\eta_{CONTROL}) = 98.83\%$

(@ TON\_max η = 600ns (max. η), S3\_GD =27pJ, S4\_GD=34pJ @ Ton = 600ns for 1V5 to 3V3, 1kHz/1ms Burst Space assumed = 200pJ

July 2021

## **Timing Requirement: Nano-seconds to Hours**

For the example: P\_switching\_cycle\_optimised = 25.4 mW

from HV Buck to LV Boost

Relatively large Energy per Switching Cycle is required for low Gating and Control loss => SMALL BURST DUTY CYCLES

time (hours, days)

bursting may require small counter values => clock frequency flexibility

=> UNIFIED TIME BASE is required from 10s' ns to hours

- => Burst Space = 25.4 ms for 1uW Power, for one switching cycle (~us) per burst

- For a number of switching cycles per burst-mark; the burst space will be 100s milli-seconds

- INTERLEAVED SOURCES may require vastly different switching cycle on-times and duty cycles, such as

- ENERGY METROLOGY will require accurate timing during short on-pulse duration and during long off-

- Non-bursting control may be by LTI control and cater for high resolution count number. Low energy

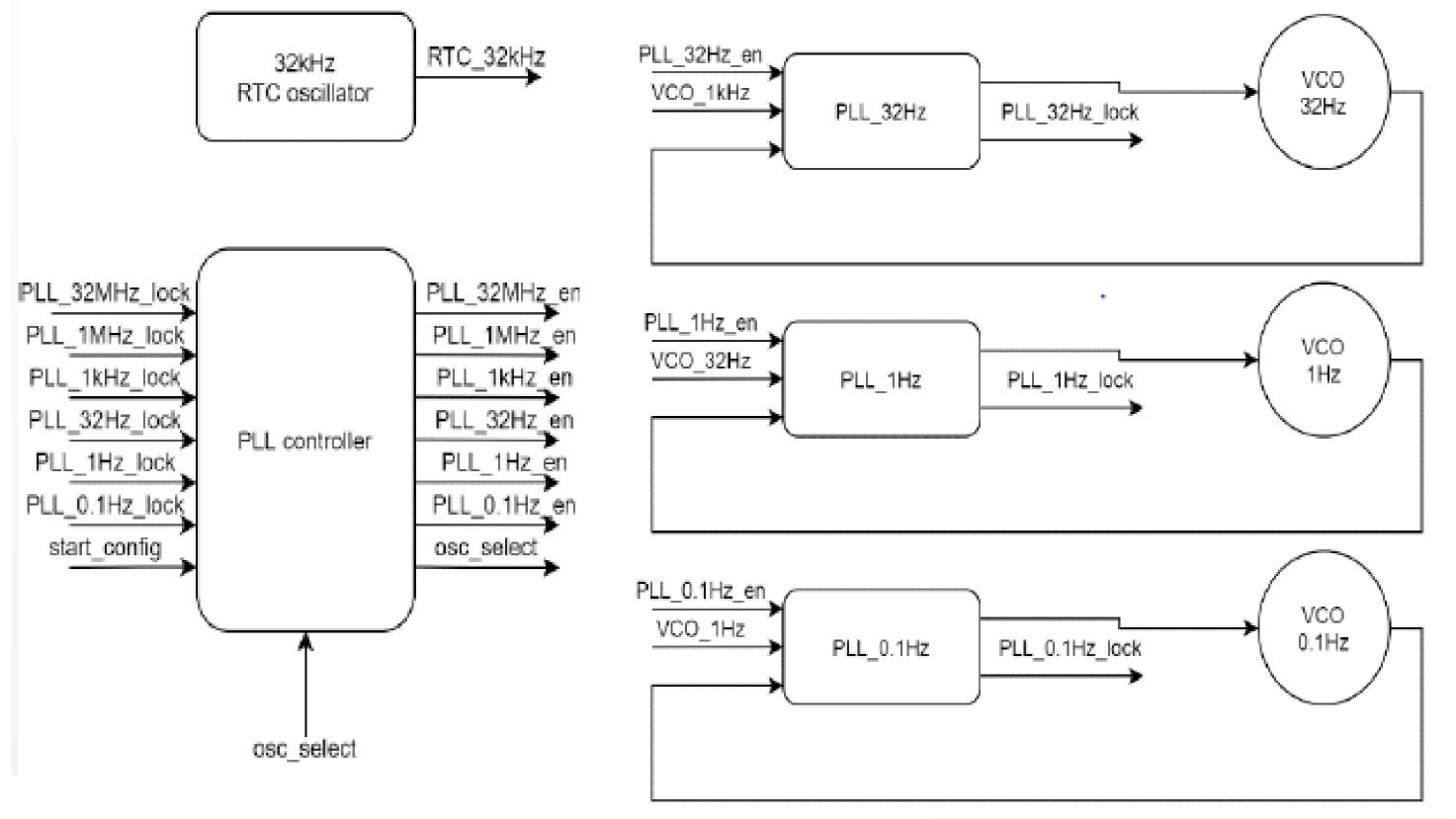

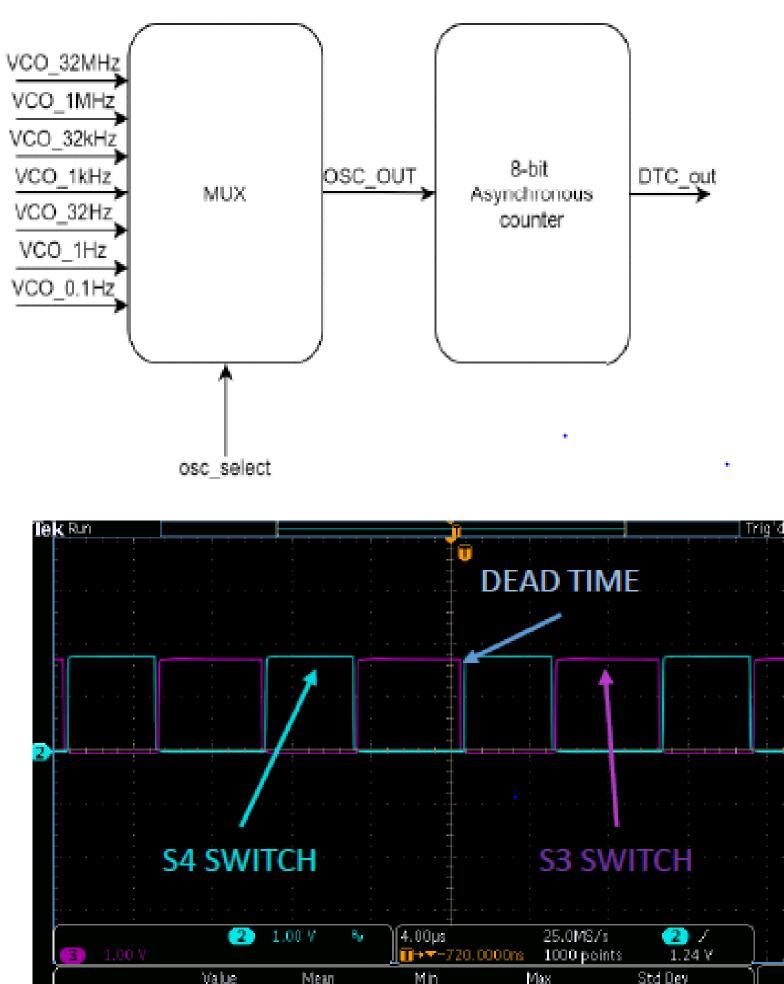

# Digital to Time Converters (DTC)

- Triggerable sequentially to build PWM or PFM Modulator Output

- Unified time base from 10 ns to hours

- Ganged system of 7 ultra low power oscillators, rapid start currentstarved oscillators

- 32 mHz to 32 MHz, and 134 MHz

- Background low energy PLL system to trim 7-Gang to the 32 kHz RTC

- 8b control over Ton

- 35b control over *Toff* or other *Wake* or *Metrology Timing* Dynamic oscillator enabling and interchange for lowest energy interval

- counter during LTI control

# DTC (PLL + LF OSC Bank + HF OSC Bank)

Energies (incl. oscillator start-up energy):

1 us - E = 244 pJ

1 ms - E = 92 pJ

10 ms - E = 306 pJ

1 s - E = 100 nJ

$$680 n$$

$680 n$

$680 n$

Tyndall: Ultra Low Power PMIC Platform

W RTC 0.1 Hz OSC

Measured Modulator Waveform with 4 DTCs in cascade, incl. 134 MHz Delay Counters

820.3µ

773.4µ

890. Sµ

Amplitude

Amplitude

781.3µV

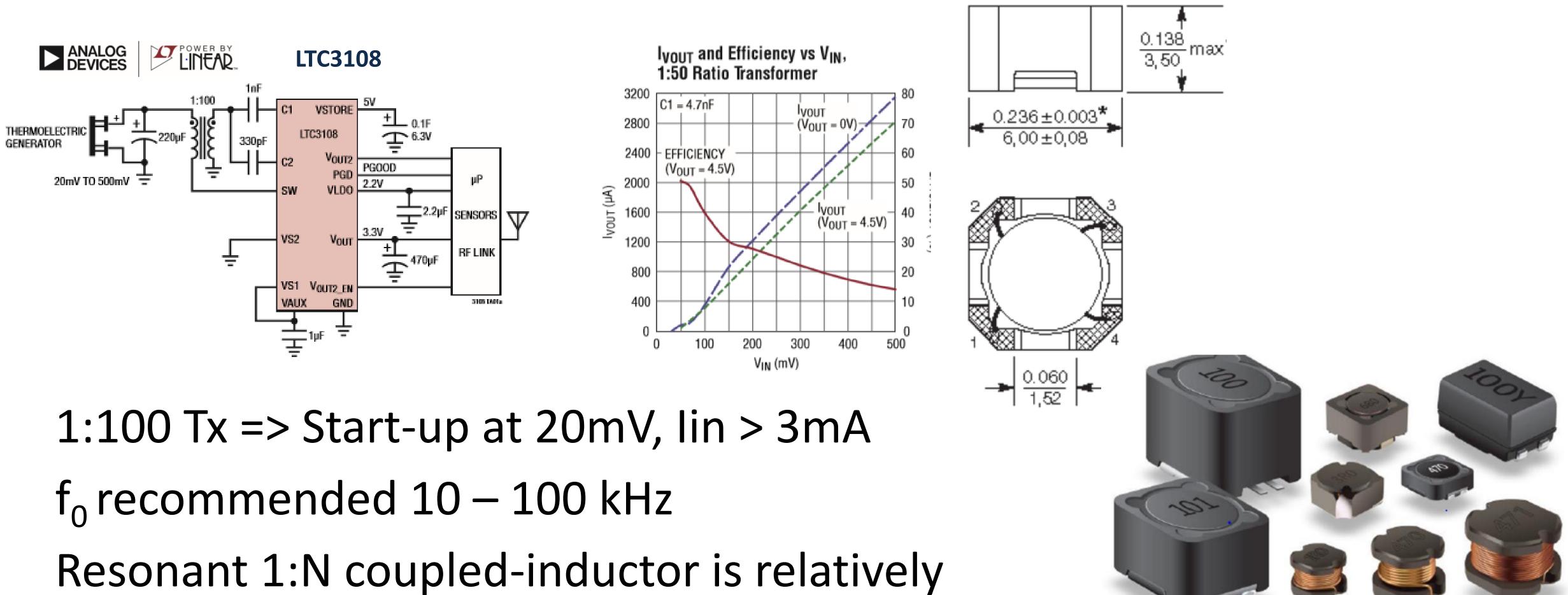

# **Commercial Low Voltage Cold Start**

huge at 6 X 6 X 3.5 mm

Tyndall: Ultra Low Power PMIC Platform

https://www.analog.com/media/en/technical-documentation/data-sheets/LTC3108.pdf

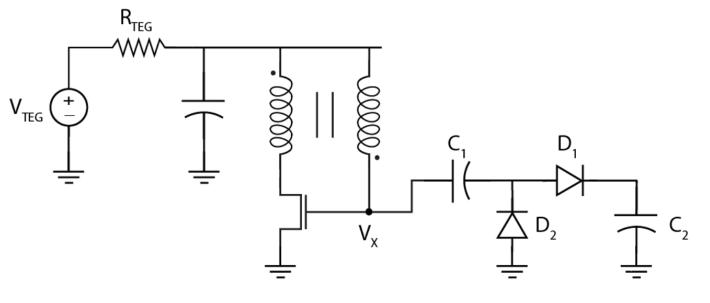

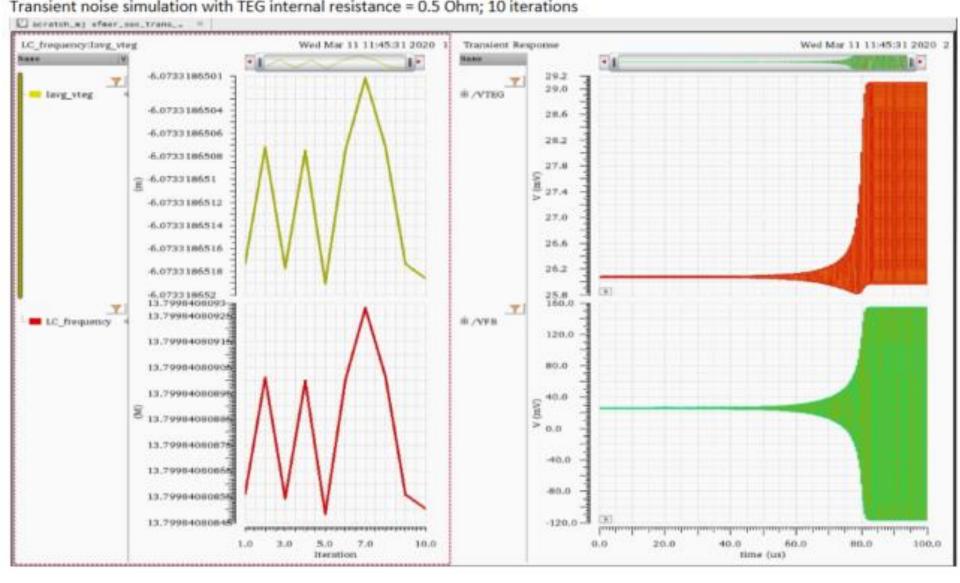

# 4:40 tf-MoS Meissner Oscillator based:

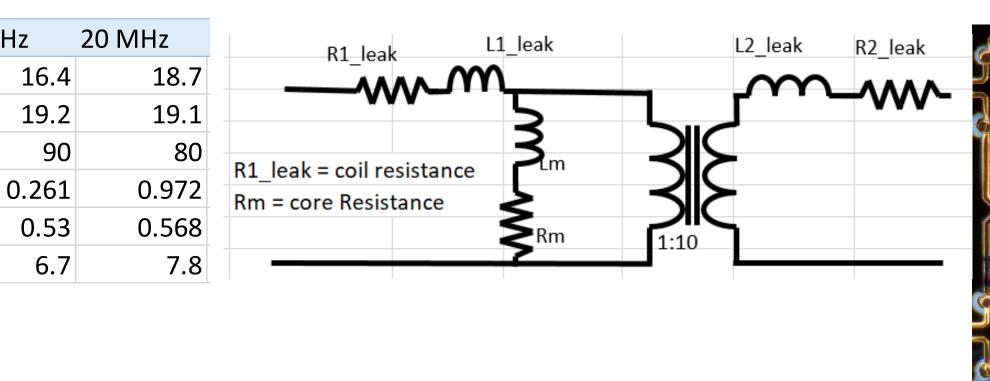

|               | 100 Hz | 15 Mł |

|---------------|--------|-------|

| Lm [nH]       | 4      |       |

| L1_leak [nH]  | 4      |       |

| L2_leak [nH]  | 100    |       |

| Rm [Ohm]      | 0.001  |       |

| R1_leak [Ohm] | 0.049  |       |

| R2_leak [Ohm] | 0.8    |       |

Meissner Oscillator [12]

180 nm CMOS *simulation* using measured S Parameter Model:

> 14 MHz =  $f_0$ 4.2 mA lin @ 30 mV (SCH) 200 X 100 um Dep. Device k ~ 0.65

"Ultra-low loss integrated magnetics platform for high frequency power delivery networks", Pranay Podder et al., Tyndall, Chor Shu Cheng et al., Global Foundries, 11<sup>th</sup> International Conference on Integrated Power Electronic Systems; Berlin, Germany. March24-26th, 2020

IS505.7 PwrSoC: Industry Adoption in High Volume Applications, APEC 2022

Tyndall: Ultra Low Power PMIC Platform

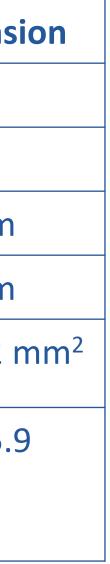

| Feature                   | Dimen                       |

|---------------------------|-----------------------------|

| Cu trace width            | 80 um                       |

| Cu trace thickness        | 16 um                       |

| Via diameter              | 100 um                      |

| Bond-pad diameter         | 160 um                      |

| Die size after dicing     | 4 × 5.2                     |

| Die size before<br>dicing | 4.6 × 5.<br>mm <sup>2</sup> |

**ENGRES** EU H2020 Grant No. 730957

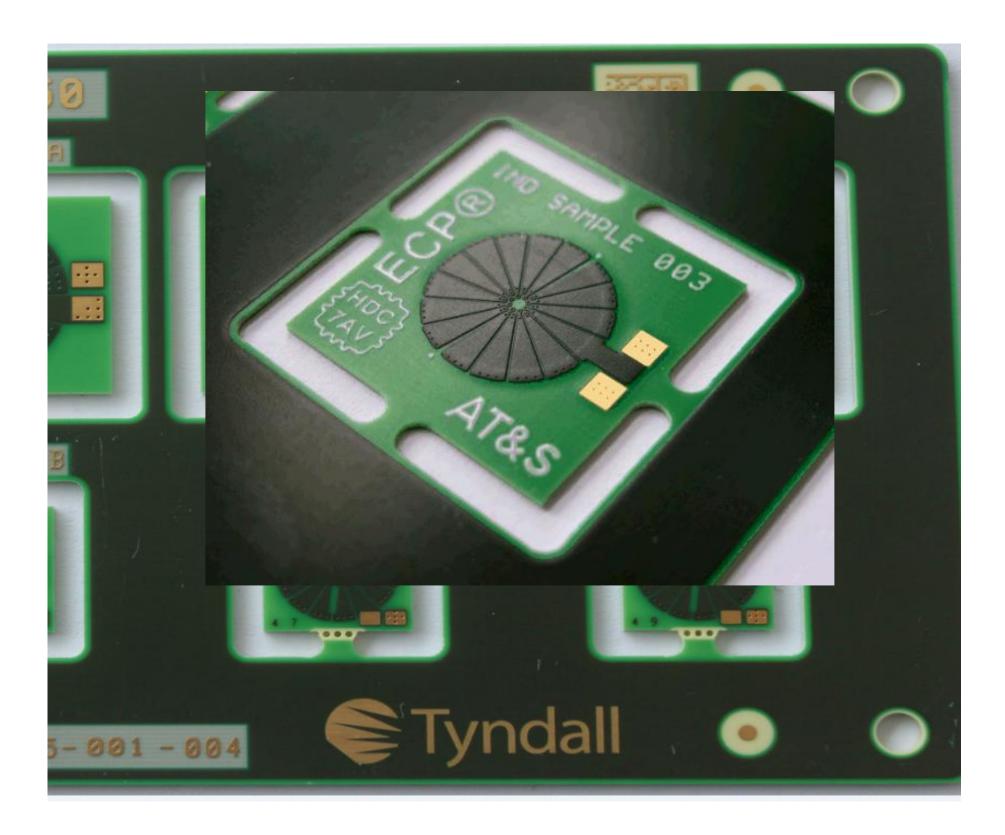

### Tyndall Cold –Start transformers

R. Murphy, Tyndall, et al., G. Weidinger et al., AT&S, EU H2020 "GaNonCMOS" www.ganoncmos.eu, CIPS2020 "High Frequency Magnetic Sheet Materials – Performance Factor Comparisons and Design of Toroidal Inductors Embedded in PCB", Ruaidhrí Murphy et al. APEC 2021

- PCB Embeddable Planar Toroidal Inductor

- Simulated this version not fabricated

- 1:100 shown, 4 mm X 17 mm, (1:40 is half size)

- Commercial magnetic material

- I<sub>MAG</sub> = 2mA, lin = 6.6 mA, 7.5 MHz, Vin= 20mV (SCH SIM)

# **COLD-START:**

Get the system going from low, unregulated voltage

|                             | MoS Transformer<br>based Oscillator | ECP transformer<br>based oscillator | LC tank based<br>Oscillator  | <b>Ring Oscillator</b> |

|-----------------------------|-------------------------------------|-------------------------------------|------------------------------|------------------------|

| On-chip area                | 2mm x 1mm<br>6mm x 4.5mm            | 2mm x 1mm                           | 2mm x 1mm                    | 3mm x 1mm              |

| Off-chip area               | None                                | 16mm x 4mm<br>(PCB embedded)        | 16mm x 4mm<br>(PCB embedded) | None                   |

| Vstart-up                   | 80 mV                               | 40 mV                               | 150 mV                       | 175 mV                 |

| Power required for start-up | 480 uW                              | 240 uW                              | 15 uW                        | 5.3 uW                 |

### Status:

#### On-chip 380 mV block taped out in H1M2 EnABLES JRA CC 01/06/2021 3 blocks at Schematic PVT to tape-out H2M3 Q1 2022

## DYNAMIC BANDGAP REFERENCE

Powers Up, Settles and drives *Dynamic Hysteretic Voltage Sense* Or *12 bit Precision Differential SAR ADC*

~ 15 uA for 15 us = 225 pJ

Tyndall: Ultra Low Power PMIC Platform

VHIGH DETECT\_OUT COMP\_OUT\_HIGH COMP\_OUT\_LOW VCOMP\_IN /SENSE REF -00 VLOW QU BITS<3:02 DECIDE\_OU REF\_OUT REFL<11:0> RESETE VSS\_SENSE

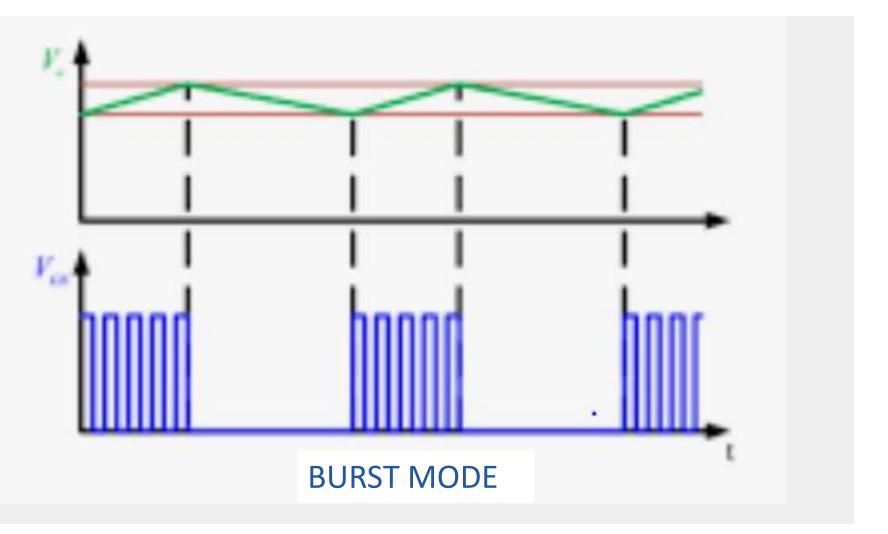

# Ultra Low Power "Mischief" PMIC PLATFORM for Energy Harvesting IoT Node

EnerHarv 2022

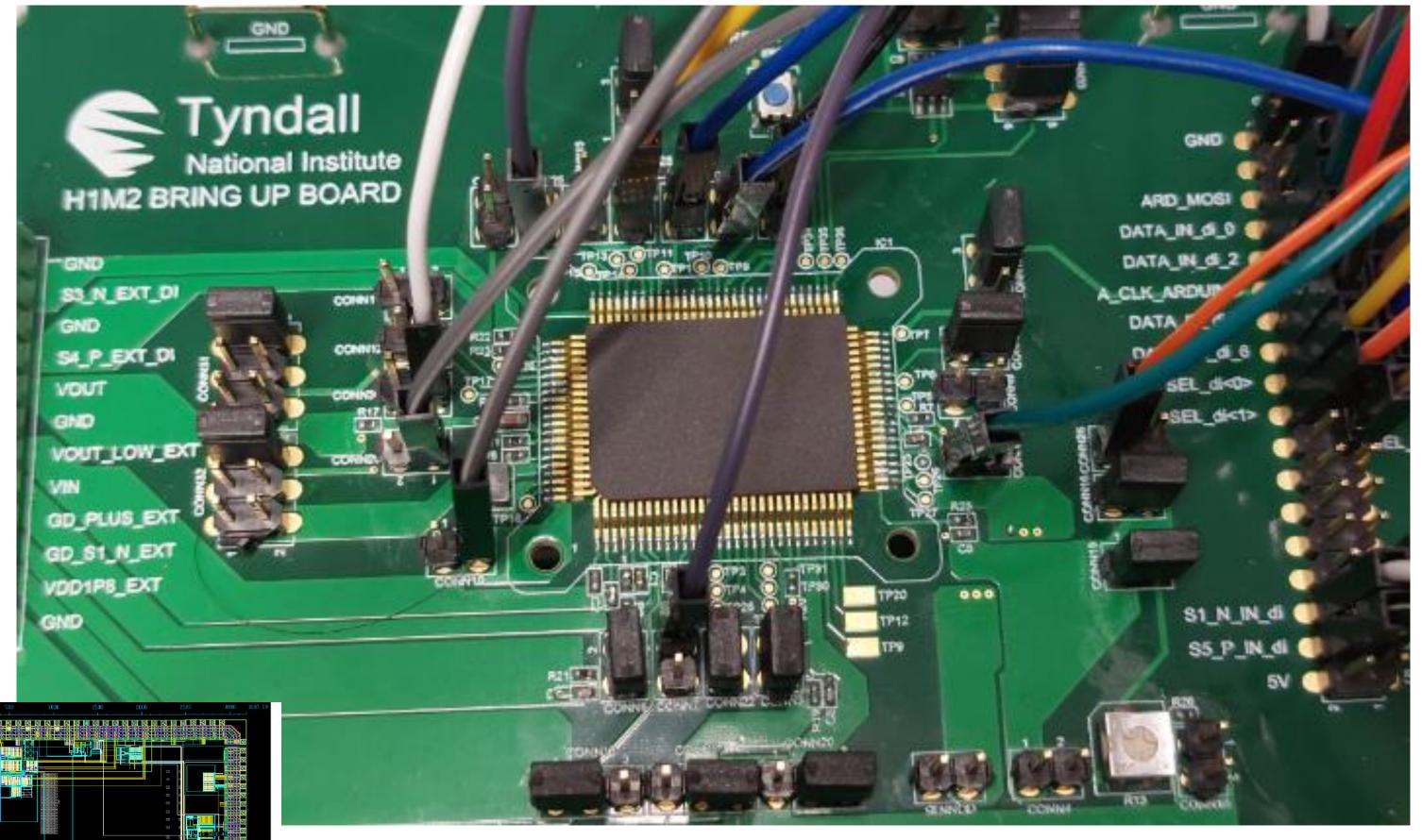

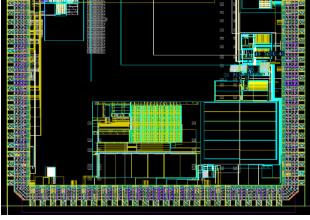

H1M2 v1 IC – Most blocks are working as intended.

RING\_VDD\_1P8 = 18 nA GD VDD 1P8 = 20 nA

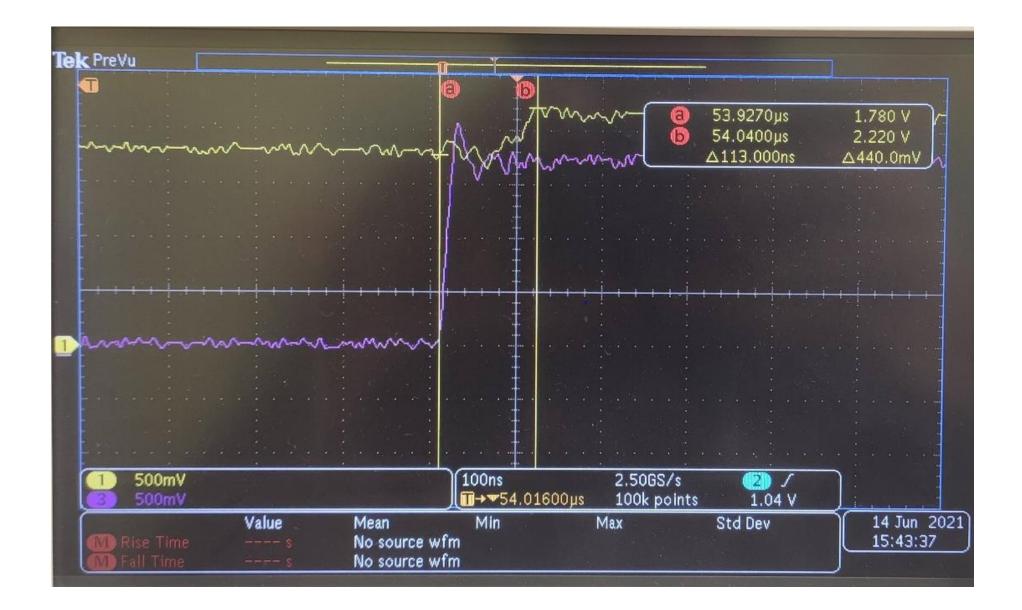

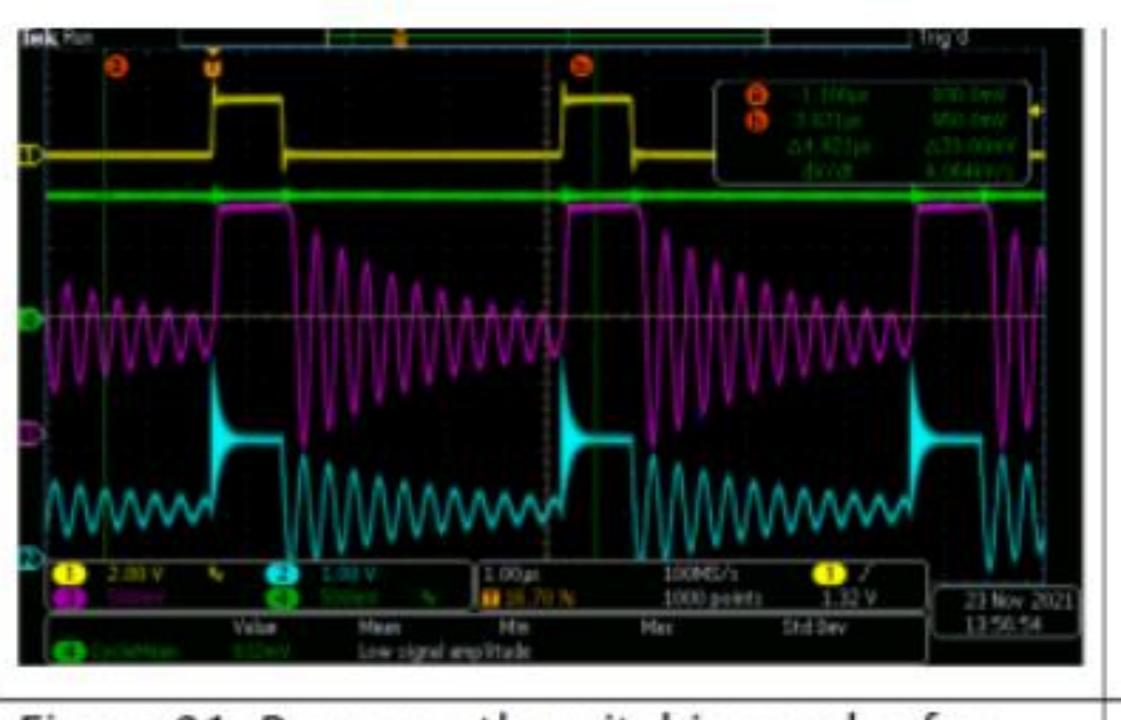

## Preliminary H1M2 chip tests

VHI Block: Selects the highest voltage in the system VIN, VOUT, VBIAS, V PRI BAT, V STORAGE must always be available to bias the bodies of PMOS devices by a clocked-comparator multiplexer system

Output voltage changes when VIN2 transitions to 2 V, while VIN1 is at 1V8

Figure 21: Power path switching cycles for Vin = 1.8 V (modulating signal - yellow, Output voltage – green, VSN1 – cyan, VSN2 magenta)

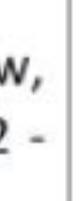

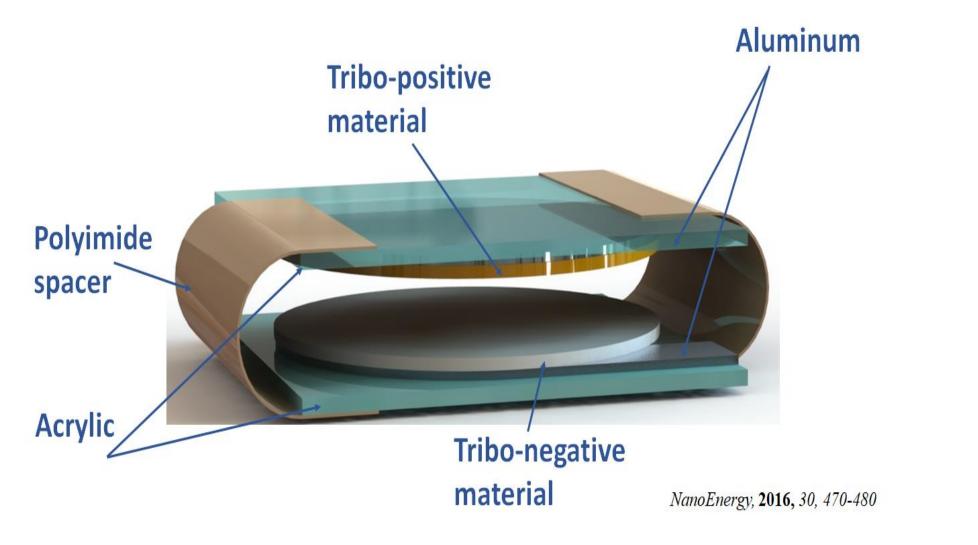

## **Tribo-electric Generator - TENG Engles** TA 051 Dr Navneet Soin, Ulster University

https://pubs.rsc.org/en/content/articlelanding/fd/2014/c4fd00159a#!divAbstract https://www.sciencedirect.com/science/article/pii/S221128551930998X https://www.sciencedirect.com/science/article/abs/pii/S2211285518300430 https://pubs.acs.org/doi/abs/10.1021/acsami.7b18442 https://www.sciencedirect.com/science/article/abs/pii/S221128551630458X

Voltage (V)

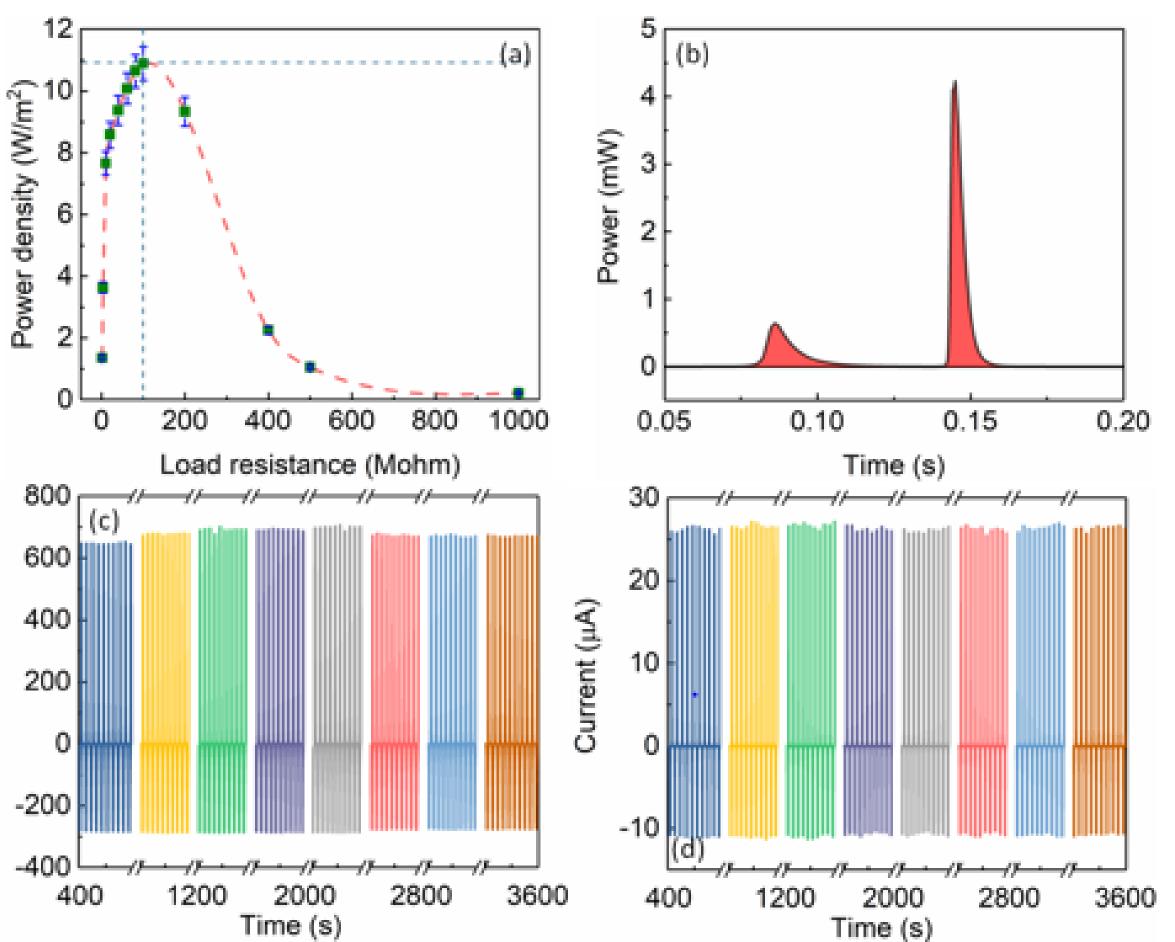

## CLAMPED 200 V DIODE BRIDGE + 200 V Buck Styndall Converter Using XFAB 180 SOI: 200 V SJ FETs and Diodes & Clamping to 200 V

### 200 V Bridge Rectifier

200 V Clamp

Tyndall: Ultra Low Power PMIC Platform

200 V, 30 kHz Buck Converter 4 mW 80 % efficient

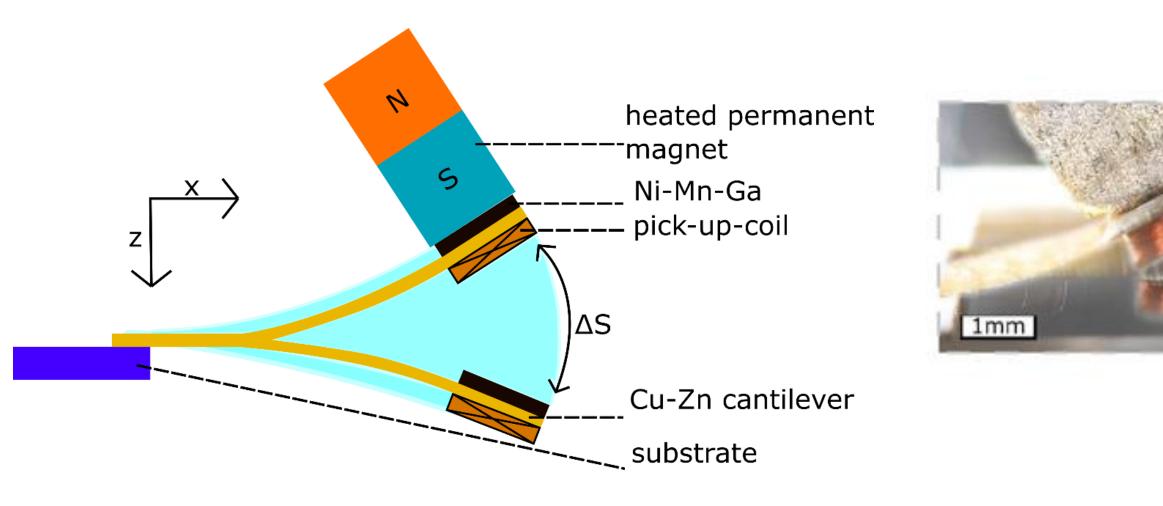

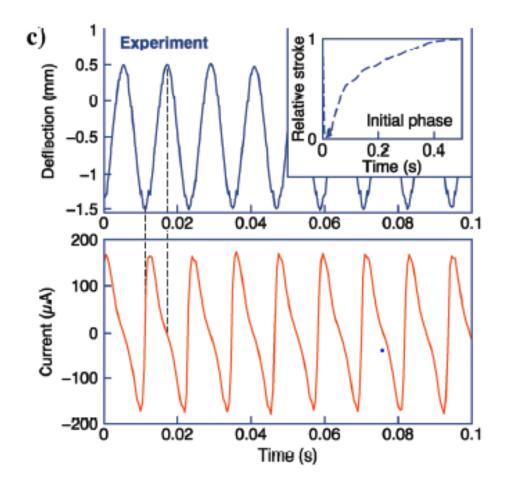

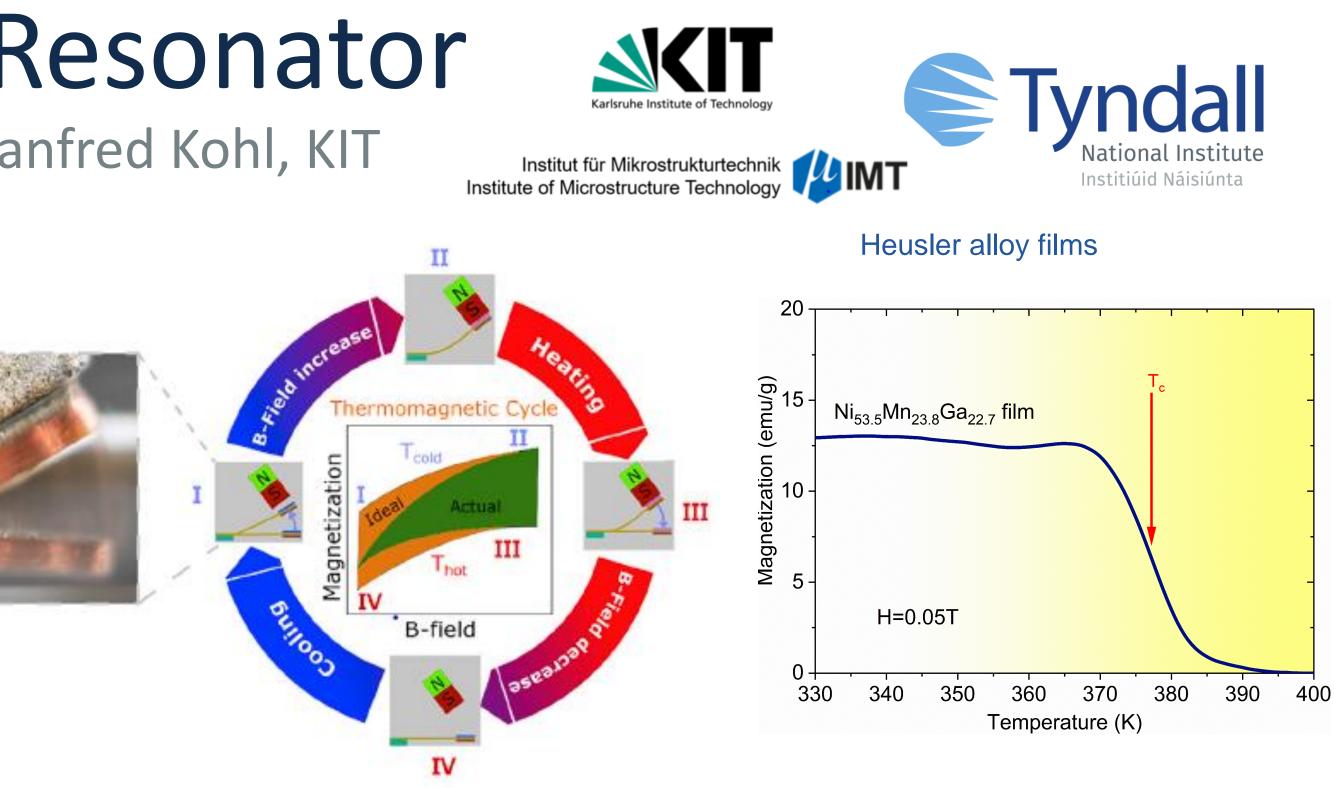

## TMG: Thermomagnetic Resonator Enables TNA\_052 Feasibility Study: Tyndall + Manfred Kohl, KIT

- with *Mischief*

Tyndall: Ultra Low Power PMIC Platform

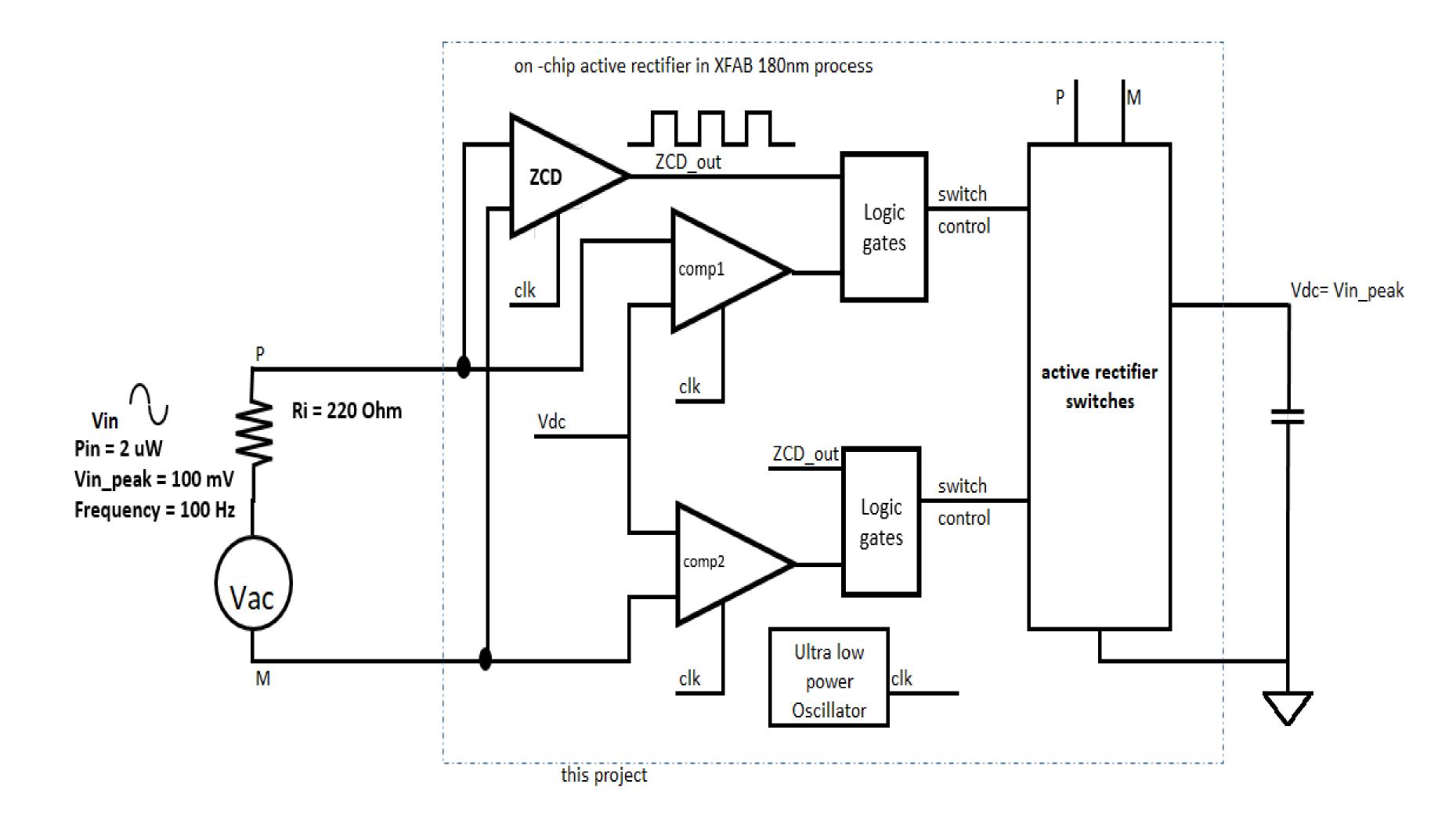

• Designing an Active Rectifier block to interface this AC voltage source

#### • Efficiently convert 10-100 mV AC, ~100 Hz, 2-5 $\mu$ W

J. Joseph, et al., Upscaling of Thermomagnetic Generators Based on Heusler Alloy Films, Joule 4,12 (2020) 2718-2732. DOI:10.1016/j.joule.2020.10.019

**ENGBLES** EU H2020 Grant No. 730957

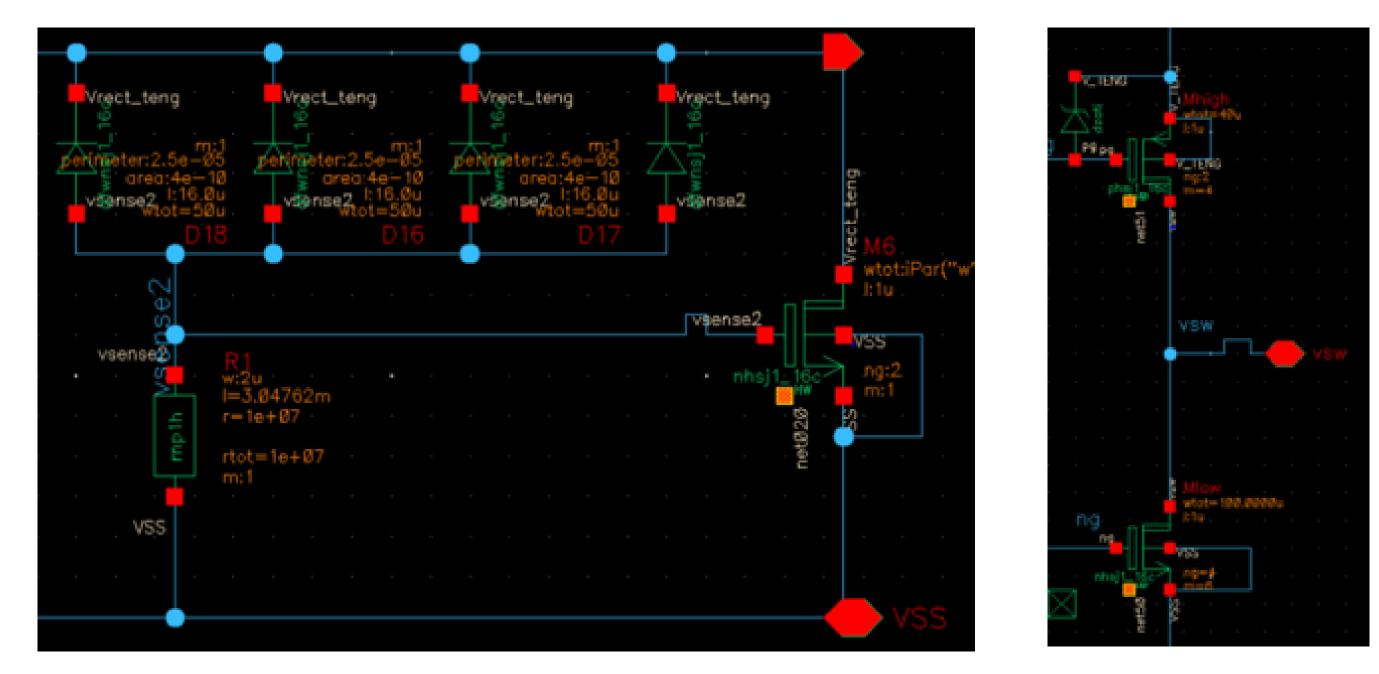

## 30 mV to 1 VAC Active Rectifier – 5uW + Styndall

Tyndall: Ultra Low Power PMIC Platform

### 100 Hz AC

### 10 kHz Clocked Comparator System

SCH level block design

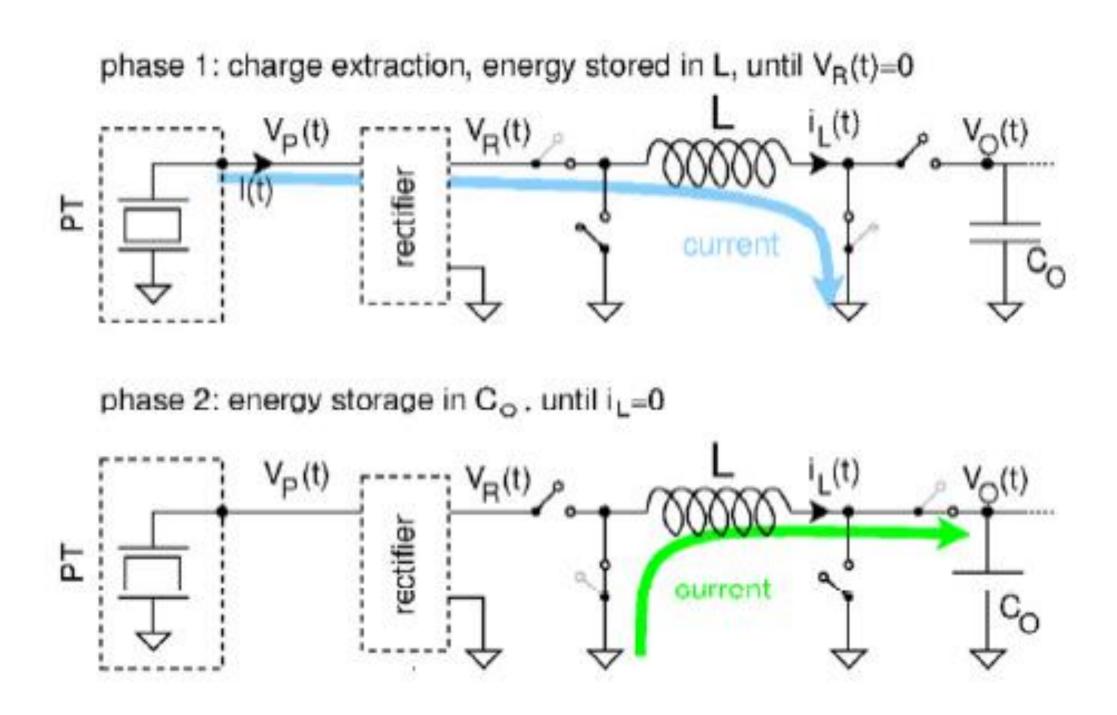

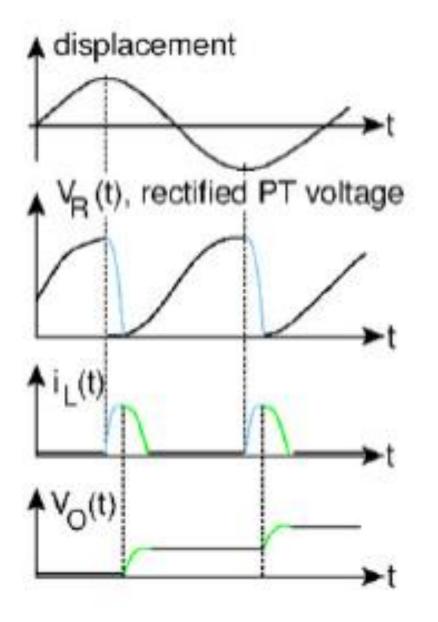

# SECE Piezo Harvesting Circuit Example

EUROSENSORS 2014, the XXVIII edition of the conference series

#### Quasi-Synchronous Charge Extraction for Improved Energy Harvesting from Highly Coupled Piezoelectric Transducers

Aldo Romani\*, Matteo Filippi

University of Bologna, Via Venezia 52, Cesena 47521, Italy

This is a Buck-Boost Circuit operated synchronously with mechanical vibration to resonantly (efficiently) extract charge from the piezo capacitive source

All of these harvesting circuits benefit from:

- MPPT

- Analog Event Driven State Machines

- Digital Timing Curcuits

- High Speed Low Threshold Comparators

- resonances

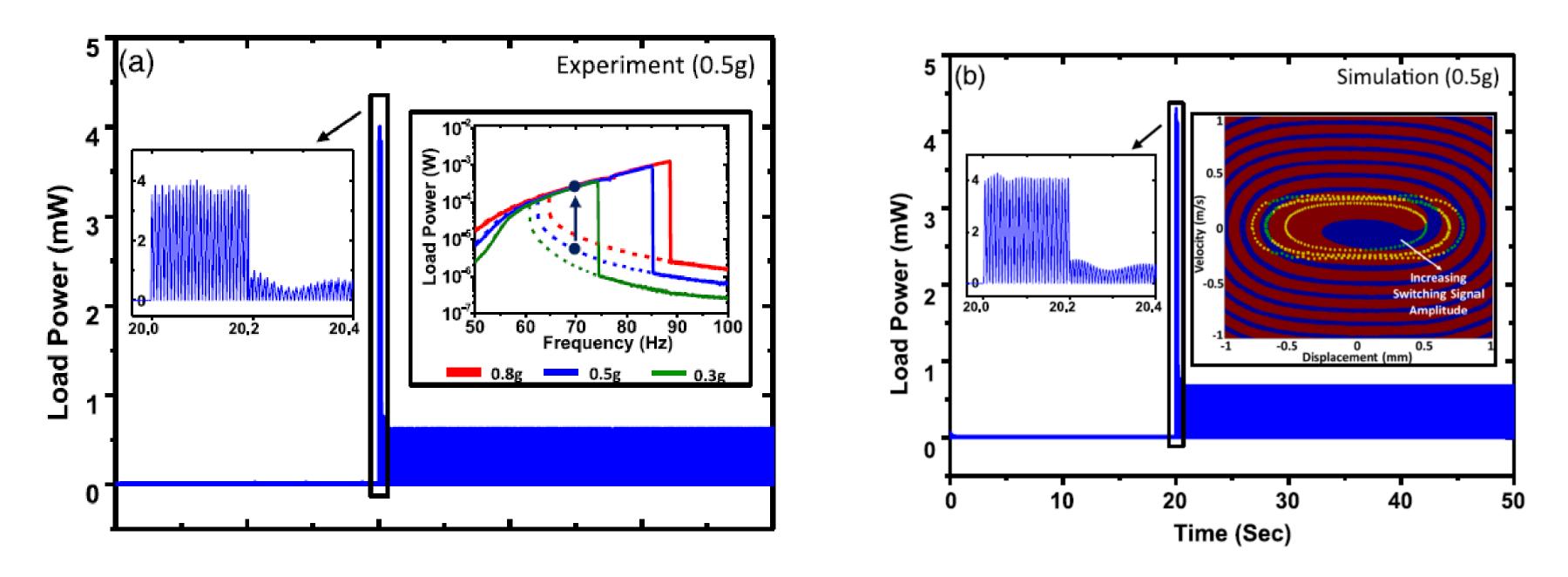

"Surfing the high energy branch of nonlinear energy harvesters', D. Mallick, S. Roy, Phys. Rev. Lett., week ending 4 NOVEMBER 2016, claim

**Example for Electromagnetic VEH**

### Mechanical Non-Linearities added in transducer design + Non-Linear Electrical Stimuli to maintain high energy branch

## Conclusions

plus new DTC/Modulator and ADC System All of the tough Analog blocks are then completed

Next stage is to seek ambitious system co-developer/ customers for a commercial prototype grade version

Top Level Application Manager (Digital Block Design)

Engineering to commercial grade platform, BIST

We welcome research collaborations and we are able to set up leveraged funding opportunities with Irish Government, EU or possibly US/Ireland Funding

- Currently we are engineering towards H2M3 version with 2nd revision blocks,

## Acknowledgements

## Michael Hayes, Brendan O'Flynn A large team Gerry McGlinchey, Andrija Stankovic, Madhu Jacob, James McCarthy, Tim Daly, Venkata Bhumireddy

Funders: Enterprise Ireland, Science Foundation Ireland, Department Enterprise, Trade and Employment (DETE DTIF)

Tyndall: Ultra Low Power PMIC Platform

Department of Enterprise, Trade and Employment

#### BACKGROUND IP PMIC Technology Blocks

FLEXIBLE POWER PATH OSCILLATORS & DTC MODULATORS BANDGAP & REFERENCES COLD START ADC . HYSTERETIC CONTROL COMPARATORS DC/ AC INPUTS/ RECTIFIERS SPI - Digital Interface DTI CONTROL 50 mV to 1 VAC Active Rectifier 5 - 200 VAC Rectifier & Buck Converter Front End

Tyndall: Ultra Low Power PMIC Platform

### FOREGROUND IP (IMT) Application ASIC

#### (IMT) APPLICATION MANAGER BLOCK (Digital)

(IMT) TOP LEVEL DESIGN - Interrconnecting Blocks

(IMT) APPLICATION BIST

APPLICATION QUALIFICATION

FABLESS SUPPLY CHAIN